【要求】

实验内容与原理说明(包括框图、逻辑表达式和真值表)。

实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。

仿真波形图。

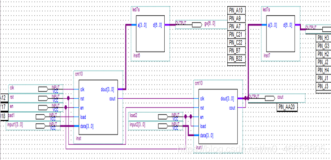

综合得到的门级电路图。

实验结果分析及思考。

每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。

【软件工具】

QuartusII;

ModelSim SE.

【一】设计一个8-3线优先编码器(74LS148)

- 实验内容与原理说明

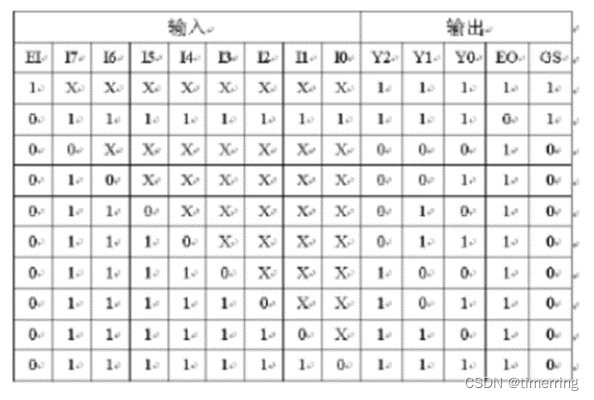

实验一为设计一个8-3线优先编码器,即可以将八个输入的编码,通过对于输入信号的分析,输出第几个信号是低电平。8线-3线优先编码器有8个输入端I0'~I7',低电平为输入有效电平;有3个输出端Y0'~Y2’,低电平为输出有效电平。此外,为了便于电路的扩展和使用的灵活,还设置有使能端S'、选通输出端Ys'和扩展端Yex'.

该设计模块的实验框图如下:

根据8-3线优先编码器可以列出其真值表如下:

2. 实验模块程序代码和激励代码

(1)设计模块代码

module Encoder83(IN, EI, GS, EO, OUT);

input [7:0] IN;

input EI;

output [2:0] OUT;

output GS;

output EO;

reg [2:0] OUT;

reg GS, EO;

always @(IN or EI)

if(EI) begin OUT <= 3'b111; GS <= 1; EO <= 1; end

else if (IN[7] == 0) begin OUT <= 3'b000; GS <= 0; EO <= 1; end

else if (IN[6] == 0) begin OUT <= 3'b001; GS <= 0; EO <= 1; end

else if (IN[5] == 0) begin OUT <= 3'b010; GS <= 0; EO <= 1; end

else if (IN[4] == 0) begin OUT <= 3'b011; GS <= 0; EO <= 1; end

else if (IN[3] == 0) begin OUT <= 3'b100; GS <= 0; EO <= 1; end

else if (IN[2] == 0) begin OUT <= 3'b101; GS <= 0; EO <= 1; end

else if (IN[1] == 0) begin OUT <= 3'b110; GS <= 0; EO <= 1; end

else if (IN[0] == 0) begin OUT <= 3'b111; GS <= 0; EO <= 1; end

else if (IN == 8'b11111111) begin OUT <= 3'b111; GS <= 1; EO <= 0; end

else begin OUT <= 3'b111; GS <= 1; EO <= 1; end endmodule

(2)激励模块代码

// Verilog Test Bench template for design : Encoder83

//

// Simulation tool : ModelSim (Verilog)

//

`timescale 1 ps/ 1 ps

module Encoder83_vlg_tst();

reg EI;

reg [7:0] IN;

wire EO;

wire GS;

wire [2:0] OUT;

Encoder83 i1 (.EI(EI), .EO(EO), .GS(GS), .IN(IN), .OUT(OUT));

initial

begin

EI = 1;

IN = 8'b11111111;

#10 EI = 0;

#10 IN = 8'b01010101;

#10 IN = 8'b10101010;

#10 IN = 8'b11010101;

#10 IN = 8'b11101010;

#10 IN = 8'b11110101;

#10 IN = 8'b11111010;

#10 IN = 8'b11111101;

#10 IN = 8'b11111110;

#10 IN = 8'b11111111;

end endmodule

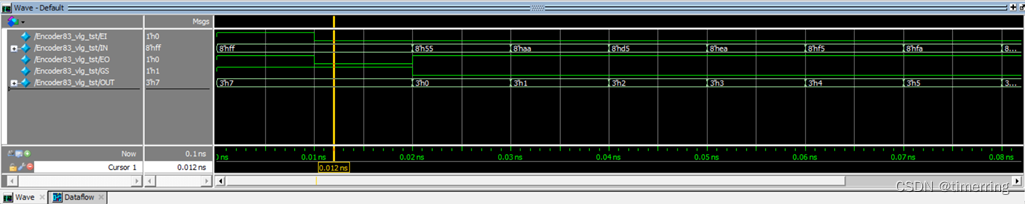

- 波形仿真图

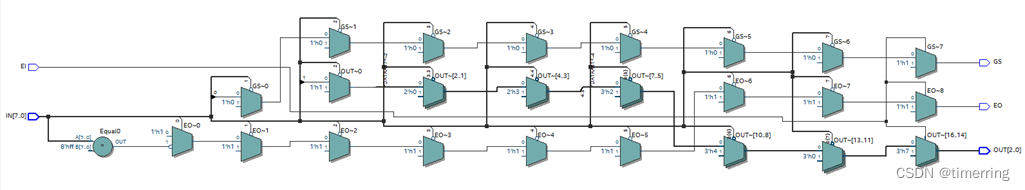

4.门级电路图

【二】设计一个3-8线译码器(74LS138)

- 实验内容与原理说明

实验二为设计一个3-8线译码器。74LS138译码器的逻辑电路图和真值表如下所示,输出为低电平有效。从74LS138译码器的逻辑电路图可以看出,它具有三个附加的控制端G1、G2A、和G2B。当G1=1、G2A+G2B=0的时候,译码器将处在译码工作状态;否则译码器将被禁止,所有的输出端将被封锁在高电平,如真值表所示。实际上,这三个输出端也可叫做“片选”输入端,利用片选的作用可以将多片74LS138译码器连接起来以扩展译码器的功能,例如用两片74LS138可以连接成一个四线—十六线译码器。即将输入的三位二进制数根据一定的准则进行译码,输出八位二进制数,所代表的一位输出是高电平,其他的输出为低电平。

其封装后的实验框图如下所示:

对应74LS138译码器的真值表如下所示:

2. 实验模块程序代码和激励代码

(1)设计模块代码

module Decoder38(OUT,IN);

input [2:0]IN;

output reg [7:0]OUT;

always@(IN)

begin

case(IN)

3'b000:OUT=8'b1111_1110;

3'b001:OUT=8'b1111_1101;

3'b010:OUT=8'b1111_1011;

3'b011:OUT=8'b1111_0111;

3'b100:OUT=8'b1110_1111;

3'b101:OUT=8'b1101_1111;

3'b110:OUT=8'b1011_1111;

3'b111:OUT=8'b0111_1111;

default:OUT=8'b1111_1111;

endcase

end

endmodule

(2)激励模块代码

// Verilog Test Bench template for design : Decoder38

//

// Simulation tool : ModelSim (Verilog)

//

`timescale 1 ps/ 1 ps

module Decoder38_vlg_tst();

reg eachvec;

reg [2:0] IN;

wire [7:0] OUT;

Decoder38 i1 (

// port map - connection between master ports and signals/registers

.IN(IN),

.OUT(OUT) );

initial

begin

IN=3'b000;

5 IN=3'b001;

5 IN=3'b010;

5 IN=3'b011;

5 IN=3'b100;

5 IN=3'b101;

5 IN=3'b110;

5 IN=3'b111;

end

endmodule

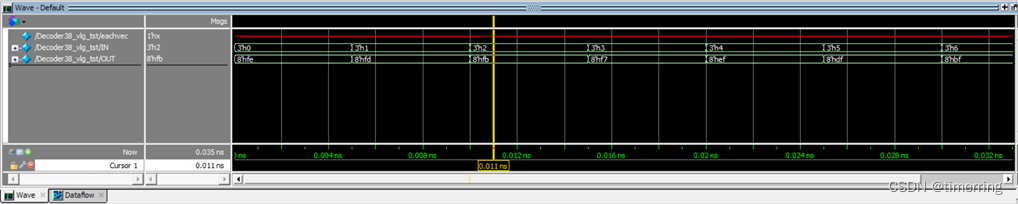

- 波形仿真图

4.门级电路图

【实验结果分析及思考】

本次实验主要设计8-3线优先编码器与3-8线译码器,这让我复习到了数电中所学过的相关知识,对于优先编码器74LS148是带有扩展功能的8-3线优先编码器,它有8个信号输入端,3个二进制码输出端,一个输入使能端,一个选通输出端和一个扩展端。使能端为“0”时,该芯片被选中,否则不被选中。选通输出端和扩展端主要用于功能扩展。,普通的二进制编码器要求在任意时刻仅能由一个输入端有效,当同时有两个或更多输入信号有效时,输出将会变得混乱,因此普通的编码器会收到一定的限制,为了克服这种限制提出了优先编码器。优先编码器允许多个输入信号同时有效,但它只对其中优先级别最高的有效输入信号编码,对级别低的输入信号则无视。3-8线译码器则是当一个选通端(S0)为高电平,另两个选通端((/S1))和(/S2))为低电平时,可将地址端(A0、A1、A2)的二进制编码在 Y0 至 Y7 对应的输出端以低电平译出。(即输出为 Y0 至 Y7 的非)比如:A2A1A0=110 时,则 Y6 输出端输出低电平信号。

综上,本次实验在参考部分书上讲解之后,自己采用行为描述的方法,不同于书上的casez和for的实现,我采用了if和else的进行了编码尝试,最终效果良好,此次实验相较于上次实验,我对于软件的使用较为熟练,在编写激励模块代码时考虑的也更为周到,但是设计的细节还需要进一步地练习与精进。