前言

阿里云虚拟化团队异构计算和高性能计算团队一直致力于将计算资源"平民化";平民化这个词我第一次是从高性能计算团队何万青老师那边听到的,他们在做的E-HPC就是要让所有云上用户都能够瞬间拥有一个小型的超算集群,使得使用超算不再仅仅是一些超算中心和高校的特权;我们异构计算团队则致力于将目前最快,最新的计算设备在云上提供给用户,之前的产品为GPU云服务器EGS;大概半年前我们正式推出了FPGA云服务器FaaS;经过内测,公测,现在终于正式上线,用户只需要开通白名单就可以和使用ECS虚拟机一样使用FPGA资源了!

FaaS介绍

FaaS,全名FPGA as a Service,是一种在云上使用FPGA的方式;我们现在支持两种不同的实例,分别为:

| 实例型号 | FPGA型号 |

|---|---|

| F1 | intel A10 |

| F2 | Xilinx ku115 |

F2从入门到放弃

准备

新建子帐号(可选)

建议用户新建一个子帐号,并使用子帐号来操作阿里云资源,通过授权子帐号必要的权限,来保证安全!

- 在左侧边栏位置选择[用户管理] -> [新建用户]

- 在弹出的创建用户的表单中填写:用户名,显示名,邮箱,电话等信息,选中为该用户自动生成AccessKey,点击确定

- 在弹出的窗口中保存用户的AK/AS,这里请一定要记住AK/AS,后续操作都会需要用到这个信息!

- 至此,RAM子帐号已经创建好,接下来需要给该子帐号授权!

- 在RAM控制台里,选中左侧的[用户管理]标签,可以看到刚刚新建的RAM子帐号,点击[授权]按钮,进行子帐号授权

- 至少给该子帐号授予如下权限:AliyunOSSFullAccess, AliyunECSFullAccess, AliyunRAMFullAccess & AliyunSTSAssumeRoleAccess;选中后点击确定即可

开通OSS,并创建一个专用的bucket

FaaS的镜像相关操作依赖于阿里云OSS存储,因此用户必须开通OSS服务;同时我们建议用户新建一个专有的bucket,用来存储您自己的FPGA镜像中间结果

开通OSS(如果已经开通请忽略这一步)

- 登陆OSS售卖页面,点击立即开通

在华东1区新建一个bucket

建议用户新建一个bucket,专门用于FaaS服务,因此这个bucket会对aliyun官方管理帐号开通读写权限,因此不建议用户存储和FaaS不相关内容;请记住这个bucket名字,在后续操作中会经常用到

- 登陆OSS管理控制台

- 点击左上方的"+"号,新建一个bucket

- 在右侧弹出的对话框中给这个bucket起一个名字,选择区域为华东1,点击确定

- 可以在左侧看到刚刚创建的bucket

购买

To 预算比较紧张,购买按量付费的用户: 考虑到F2实例价格比普通ECS价格高一些,因此建议用户在调试,编译阶段采用普通ECS;建议使用阿里云计算型实例,4核以上;在完成调试和编译后,真正需要下载到FPGA里运行时,再购买F2实例;

- 目前购买F2实例仍然需要开白名单,请用户提工单(或者联系阿里云BD)提供自己的阿里云帐号

- 开通白名单后,在阿里云官网购买页面直接购买,请选择华东1,可用区B,VPC网络;F2目前支持按量付费和包年包月两种售卖方式;实例规格请选择异构计算,FPGA计算型

- Xilinx的开发环境,我们准备了一个镜像,用户直接使用该镜像创建实例即可;该镜像后期会在镜像市场免费提供给用户,目前还只能通过共享镜像的方式提供,因此用户在选择镜像时,请选择共享镜像;如果在共享镜像里看不到镜像,需要提工单(或者联系阿里云BD)

F2 实例OpenCL开发最佳实践

这里我们以使用普通计算型实例做编译和仿真,以F2实例作为最终运行为例;当然,编译和仿真也完全可以在F2实例上完成,这样更简单

编译,仿真

对于按量用户,建议使用更加便宜的普通ECS实例(建议使用计算型4核以上实例)进行编译和仿真,因为这时候不需要真正使用到FPGA;购买普通ECS实例和购买F2实例类似,只是在选择实例规格时,选择型号不同,但是依然要使用我们共享的镜像

首先配置SDx环境

source /opt/Xilinx/SDx/2017.2/settings64.sh运行SDx自带demo:

cd /opt/Xilinx/SDx/2017.2/examples/vadd

查看在当前目录下sdaccel.mk里面的platform(第60行)是否为

XDEVICE=xilinx_kcu1500_4ddr-xpr_4_0改common.mk文件

vim ../common/common.mk把第61行

CLCC_OPT += $(CLCC_OPT_LEVEL) ${DEVICE_REPO_OPT} --platform ${XDEVICE} -o ${XCLBIN} ${KERNEL_DEFS} ${KERNEL_INCS}改成

CLCC_OPT += $(CLCC_OPT_LEVEL) ${DEVICE_REPO_OPT} --platform ${XDEVICE} -o ${XCLBIN} ${KERNEL_DEFS} ${KERNEL_INCS} --xp param:compiler.acceleratorBinaryContent=dcp软件仿真

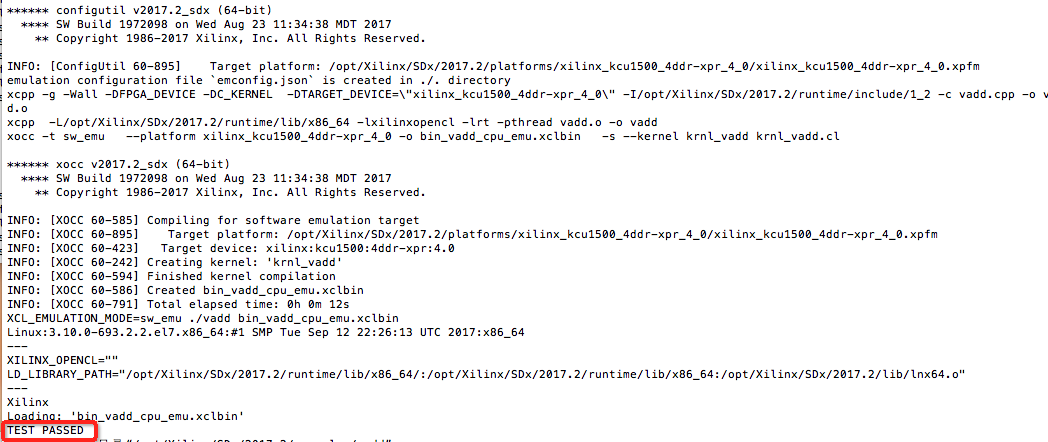

make -f sdaccel.mk run_cpu_em看结果是否PASSED

直接运行export XCL_EMULATION_MODE=true #一定要设置这个环境变量,不然会报错,找不到设备

./vadd bin_vadd_cpu_emu.xclbin

#如果报如下错:Error: Unable to find Target Device xilinx_kcu1500_4ddr-xpr_4_0;请检查XCL_EMULATION_MODE是否为true,如果没有,请设置:export XCL_EMULATION_MODE=true硬件仿真

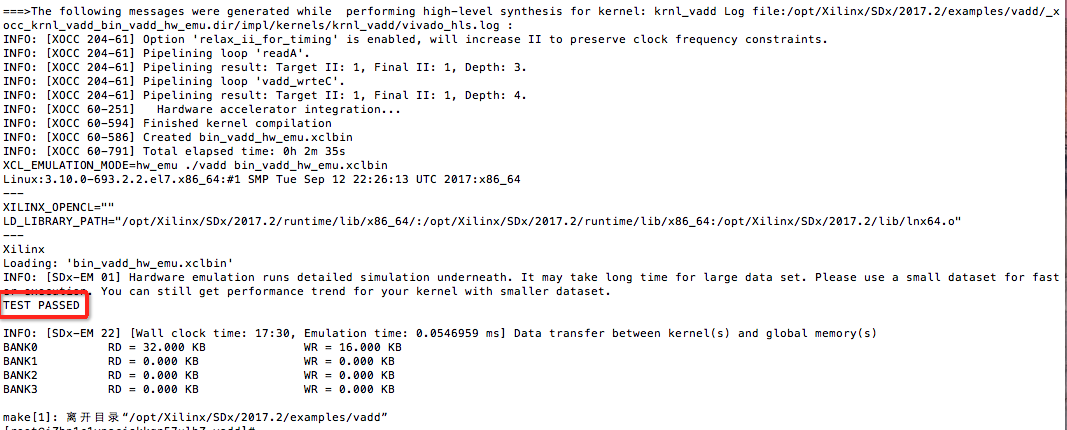

make -f sdaccel.mk cleanall

make -f sdaccel.mk run_hw_em看仿真结果是否PASSED

直接运行export XCL_EMULATION_MODE=true #一定要设置这个环境变量,不然会报错,找不到设备

./vadd bin_vadd_cpu_emu.xclbin

#如果报如下错:Error: Unable to find Target Device xilinx_kcu1500_4ddr-xpr_4_0;请检查XCL_EMULATION_MODE是否为true,如果没有,请设置:export XCL_EMULATION_MODE=true编译

make -f sdaccel.mk cleanall

make -f sdaccel.mk xbin_hw//其他一些操作

/*

make -f sdaccel.mk xbin_hw #生成最终的二进制文件,时间比较长,差不多4个小时才能完成

make -f ./sdaccel.mk help #查看帮助文档

#Compile and run CPU emulation using default xilinx:adm-pcie-7v3:1ddr:3.0 DSA

make -f sdaccel.mk run_cpu_em //即:软件仿真

#Compile and run hardware emulation using default xilinx:adm-pcie-7v3:1ddr:3.0 DSA

make -f sdaccel.mk run_hw_em //硬件仿真

#Compile host executable only

make -f sdaccel.mk host //只编译host代码

#Compile XCLBIN file for system run only

make -f sdaccel.mk xbin_hw //这个最重要,编译生成可以下载到FPGA内的二进制文件

#Clean working diretory

#make -f sdaccel.mk clean

#Super clean working directory

#make -f sdaccel.mk cleanall

*/ps:此处编译的时间会比较久,建议通过screen或者nohub等方式,防止ssh timeout退出。

配置安全烧写环境

source /root/xbinst_oem/F2_env_setup.sh faascmd config --id=<accessID> --key=<accessKey> #id/key为阿里云accessID/accessKey,上述新建子帐号曾经保存过 faascmd auth --bucket=<bucket_name> #新建的OSS bucket 名字编译成功后打包结果

#如果/root/xbinst_oem/目录里没有sdaccel_package.sh,先下载:wget http://fpga-tools.oss-cn-shanghai.aliyuncs.com/sdaccel_package.sh /root/xbinst_oem/sdaccel_package.sh -xclbin=/opt/Xilinx/SDx/2017.2/examples/vadd/bin_vadd_cpu_emu.xclbin

上传压缩包到自己的OSS指定的bucket

faascmd upload_object --object=<在bucket中名字,建议和file一致> --file=<打包生成的结果,一个tar包>新建一个可以在F2上运行的FPGA image

faascmd create_image --object=<在bucket中名字,建议和file一致> --fpgatype=xilinx --name=hereIsFPGAImageName --tags=hereIsFPGAImageTag --encrypted=false --shell=V1.0查看fpga image是否已经可以下载

faascmd list_images

我们看到状态已经是success,可以下载了。记下FPGAIamgeUUID,一会下载的时候需要用

下载

如何编译和仿真是在另外一台ECS上完成的,这里首先要购买一台F2实例;具体的购买过程参考购买章节

首先配置安全烧写环境(如果之前已经设置过,跳过)

source /root/xbinst_oem/F2_env_setup.sh faascmd config --id=<accessID> --key=<accessKey> #id/key为阿里云accessID/accessKey,上述新建子帐号曾经保存过 faascmd auth --bucket=<bucket_name> #新建的OSS bucket 名字获取fpgauuid

faascmd list_instances --instanceId=hereIsYourInstanceIdvm instance Id:可以在阿里云控制台找到

下载fpga image

faascmd download_image --instanceId=hereIsYourInstanceId --fpgauuid=hereIsFpgaUUID --fpgatype=xilinx --imageuuid=hereIsImageUUID --imagetype=afu --shell=V1.0查看是否下载成功

faascmd fpga_status --fpgauuid=hereIsFpgaUUID --instanceId=hereIsYourInstanceId

板卡上的FpgaImageUUID已经跟需要下载的image一致,并且TaskStatus已经valid,说明下载已经成功。

5.跑host程序

make -f sdaccel.mk host

unset XILINX_SDX

./vadd bin_vadd_hw.xclbin