众所周知,大多数FPGA芯片都会外挂一片Flash芯片,用于存储FPGA的程序文件。

FPGA程序下载分为两种,一种是片上调试,程序会下载到内部RAM空间,掉电程序会丢失。

另一种是程序固化,程序会下载到外部Flash芯片,一般采用的是SPI接口的Flash芯片,包括1/4/8/16位数据宽度,但不是所有型号的SPI Flash芯片都支持作为FPGA的配置芯片。

本文以Xilinx FPGA为例,介绍Xilinx FPGA ISE开发环境——iMPACT下载软件所支持的SPI Flash型号,用于硬件电路设计时外部配置芯片选型。

支持的SPI Flash芯片型号

这里指的SPI Flash一般是1位和4位数据总线的SPI Flash,

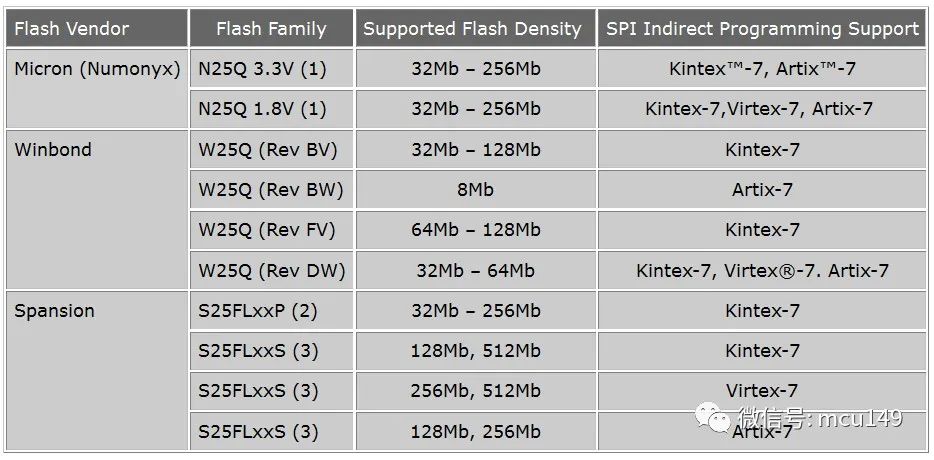

7 系列的FPGA支持的SPI Flash芯片型号

包括Kintex-7、Artix-7、Virtex-7系列。

注意:

- 支持S25FL129P、S25FL256S,不支持S25FL128P

- 只支持64KB扇区大小的Flash芯片

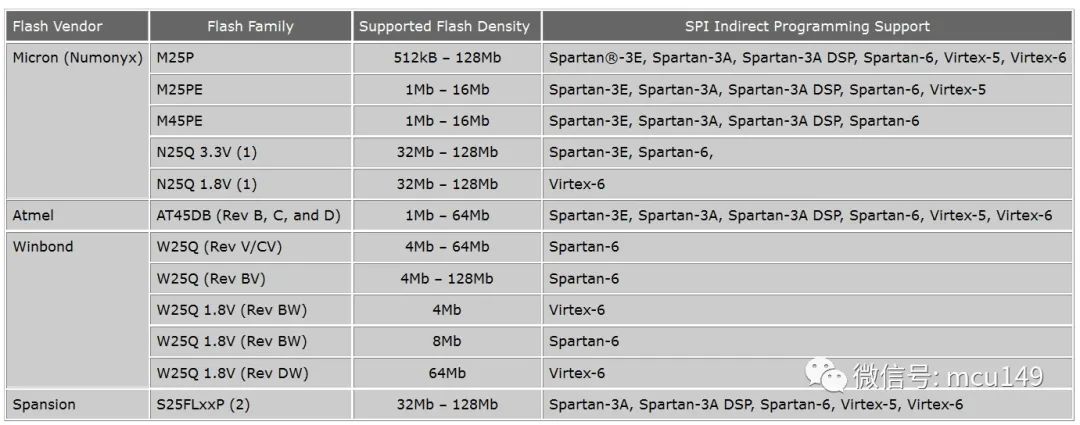

Virtex和Spartan系列支持的SPI芯片型号

主要包括Spartan-3、Spartan-6、Virtex-5、Virtex-6。

注意:

- 支持S25FL032P、S25FL064P、S25FL129P,不支持S25FL128P

- 只支持64KB扇区大小的Flash芯片

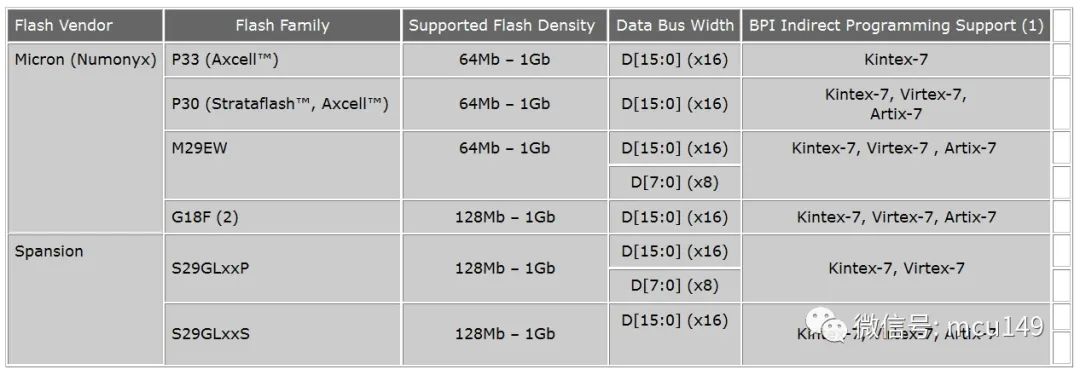

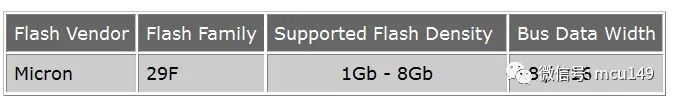

支持的BPI Flash芯片

这里指的BPI Flash(Byte Peripheral Interface)一般是8或16位数据总线的Flash芯片。

7系列支持的BPI Flash芯片型号

包括Kintex-7、Artix-7、Virtex-7系列。

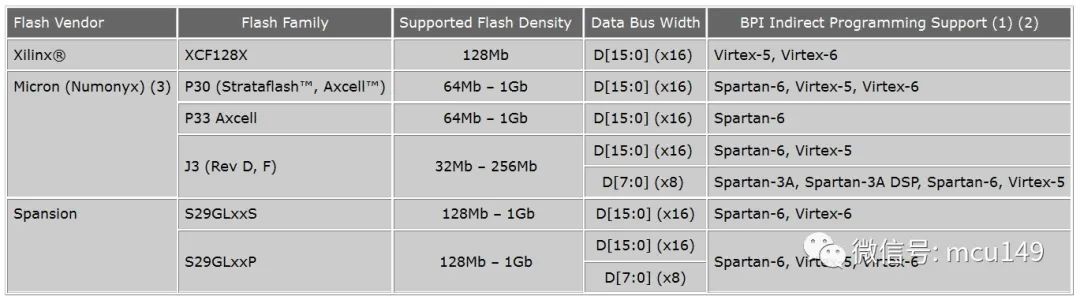

Virtex和Spartan系列支持的BPI芯片型号

主要包括Spartan-3、Spartan-6、Virtex-5、Virtex-6。

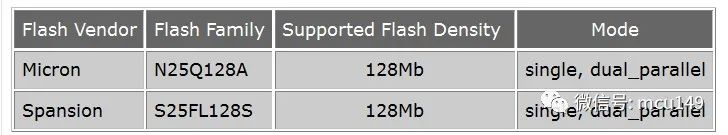

ZYNQ支持的QSPI Flash芯片型号

ZYNQ系列支持的NOR Flash芯片型号

ZYNQ系列支持的NAND Flash芯片型号