1.算法仿真效果

VIVADO2019.2仿真结果如下:

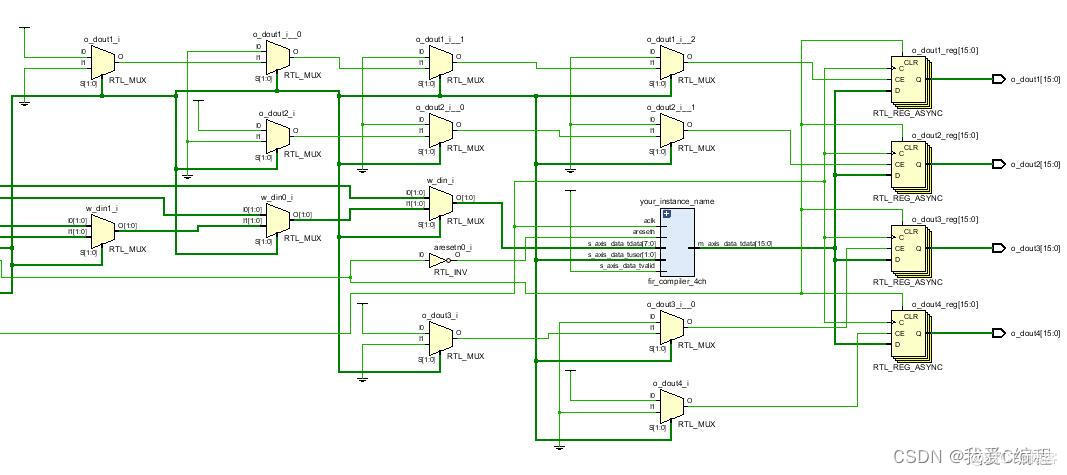

系统RTL结构如下:

2.算法涉及理论知识概要

多通道FIR(Finite Impulse Response)滤波器是一种在数字信号处理中广泛应用的线性时不变滤波技术,尤其适用于多通道音频、视频、图像等多维数据的处理。

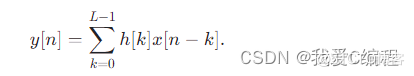

单通道FIR滤波器可由其单位脉冲响应(Impulse Response, IR)]h[n] 定义,其长度为L。对于给定的输入序列x[n],其输出y[n] 可由卷积公式给出:

多通道FIR滤波器则扩展了这一概念至多维度,处理多个并行的输入通道。每个通道都有独立的FIR滤波器,且各通道间可能存在不同的滤波特性或相互关联的处理机制。

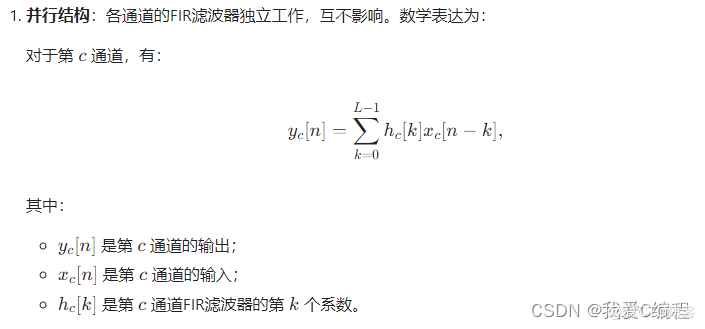

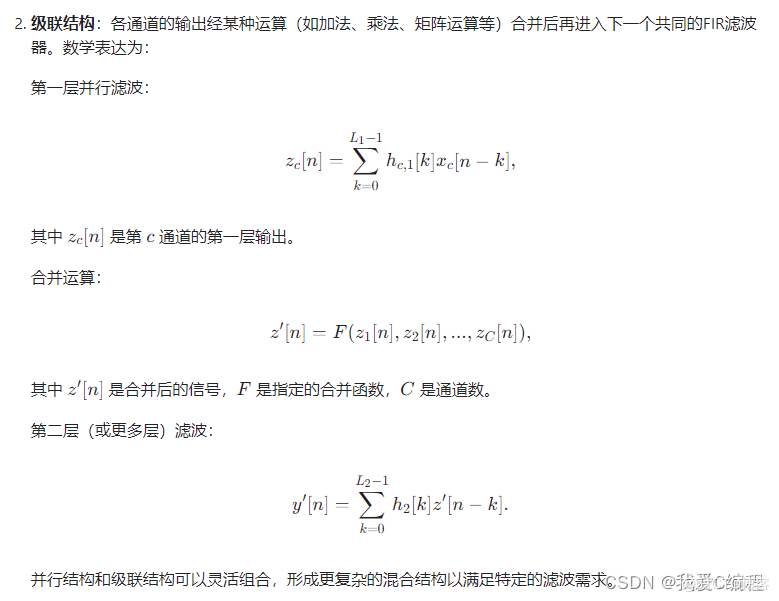

多通道FIR滤波器常见的结构包括并行结构、级联结构和混合结构。

多通道FIR滤波器的设计通常基于以下方法:

窗函数法:选择合适的窗函数(如矩形窗、汉明窗、海明窗等)与所需频率响应(如低通、高通、带通、带阻等)相结合,生成各通道的滤波器系数。

频率采样法:在数字化的频率轴上直接指定滤波器的幅值响应,再通过逆离散傅里叶变换(IDFT)得到滤波器系数。

优化算法:利用梯度下降、粒子群优化、遗传算法等优化方法,根据特定的性能指标(如最小均方误差、最大信噪比等)迭代求解滤波器系数。

机器学习方法:结合深度学习或传统机器学习算法,基于大量训练数据学习并生成各通道滤波器系数,适用于自适应滤波或复杂非线性滤波任务。

3.Verilog核心程序

````timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/03/31 21:32:24

// Design Name:

// Module Name: TEST_4CH

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST_4CH();

reg i_clk;

reg i_clk4x;

reg i_rst;

reg signed[1:0]i_din1;

reg signed[1:0]i_din2;

reg signed[1:0]i_din3;

reg signed[1:0]i_din4;

wire signed[15:0]o_dout1;

wire signed[15:0]o_dout2;

wire signed[15:0]o_dout3;

wire signed[15:0]o_dout4;

tops_4ch uut(

.i_clk (i_clk),

.i_clk4x (i_clk4x),

.i_rst (i_rst),

.i_din1 (i_din1),

.i_din2 (i_din2),

.i_din3 (i_din3),

.i_din4 (i_din4),

.o_dout1 (o_dout1),

.o_dout2 (o_dout2),

.o_dout3 (o_dout3),

.o_dout4 (o_dout4)

);

initial

begin

i_clk = 1'b1;

i_clk4x=1'b1;

i_rst=1'b1;

1000

i_rst=1'b0;

end

always #20 i_clk=~i_clk;

always #5 i_clk4x=~i_clk4x;

reg[15:0]cnt;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnt <= 16'd0;

end

else begin

cnt <= cnt + 16'd1;

end

end

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

i_din1 <= 2'd0;

i_din2 <= 2'd0;

i_din3 <= 2'd0;

i_din4 <= 2'd0;

end

else begin

i_din1 <= {cnt[3],1'b1};

i_din2 <= {cnt[4],1'b1};

i_din3 <= {cnt[5],1'b1};

i_din4 <= {cnt[6],1'b1};

end

end

endmodule

```