一. 简介

第八例啦,本例将介绍如何通过FPGA采集DS18B20传感器的温度值。

二. DS18B20简介

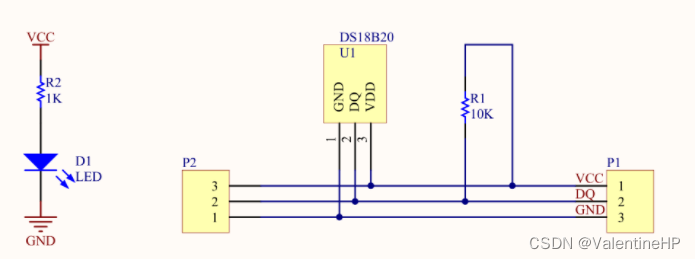

通过原理图可以看出,DS18B20温度传感器只有一条总线,可想而知,其结构的简单化,导致了其操作的复杂化。

更多关于该传感器的一些特性参数,以及性能指标,可以详细阅读官网提供的数据手册。

接下来主要讲解怎样使用它。

三. 初始化

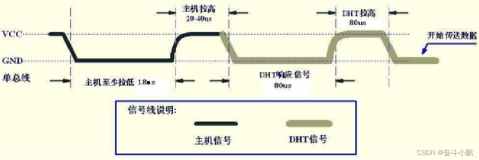

从图中可以看出,首先得由我们FPGA将总线拉低,时间为480us以上

FPGA释放总线后,再等待一个15-60us

然后会由DS18B20将总线拉低,时间为60-240us

最后DS18B20也会释放总线,等待一定时间后(从图中根据自己之前的时间可以算出),初始化完成

四. 写

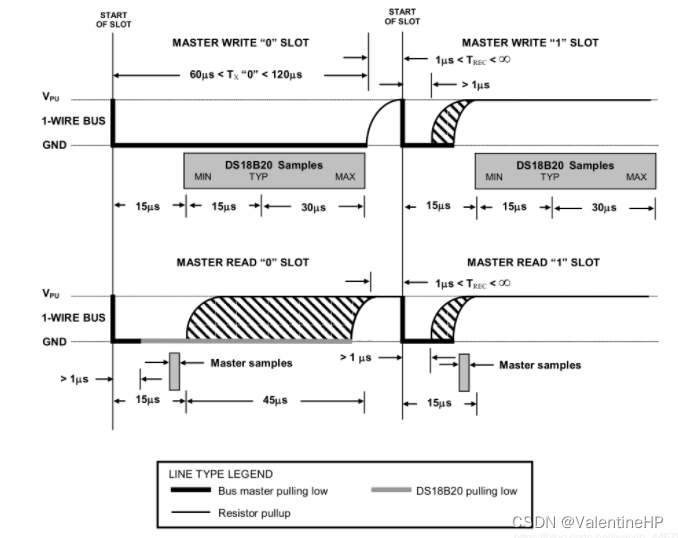

这里我们只看上面一行图,前半部分对应写0的操作,后半部分对应着写1的操作.

从图中可以得出,写每一位的时钟周期为60us,然后每一位之间的时间间隔至少为1us

写的时候,先FPGA拉低总线15us,告知DS18B20要接收数据了,然后的45us里面根据数据是0还是1,决定FPGA是将数据线拉低还是拉高

完了之后,FPAG释放总线,完成一位的数据写入

此外每写入一个字节后,最好等待50us的时间,再写下一个字节

五. 读

在第三节的那个图的第二行中,有完整的读操作时序

可以看到,读写的周期数和每位之间的间隔数完全相同,只是对应的操作稍有变化,但变化不大,先简要的说明一下

前15us为真正的读取操作,后面的45us可以不用管,FPGA直接释放总线

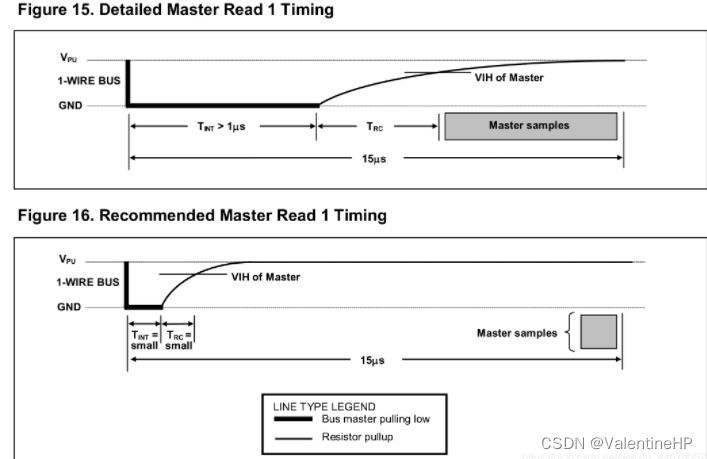

读取数据在前面的15us内完成,具体怎样可以看下面的这张图

1. FPGA先将总线拉低一个T_INT时间,可以定为1.5us 2. 然后FPGA释放总线,等待一个T_RC时间,也可以定为1.5us 3. 最后,在接下来的时间点,进行采样读取数据

读取数据的操作在此就完成了。

六. 读出数据的格式

最后再对数据的格式进行介绍一下

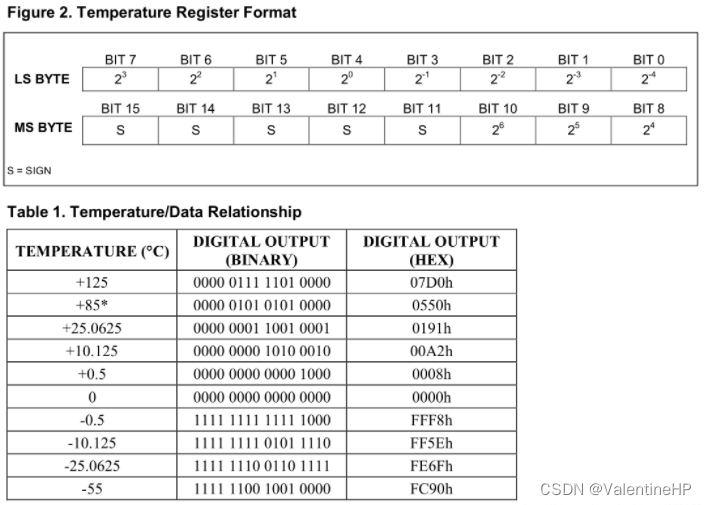

从图中可以看到,一个温度数据是16位的

在Figure2中可以看到每一位下对应着的含义,S表示符号位,1为负数,0为正数

在Table1中,可以看到一些温度值,对应着的二进制是怎样表示的,下面举例说明一下

+0.5 0000_0000_0000_1000 = 1/2 = 0.5 -0.5 1111_1111_1111_1000 = 0000_0000_0000_0111 + 1 = 0000_0000_0000_1000 = -0.5 负数在这里面是存储的补码,先要取反,然后加一,最后添负号

七. 程序

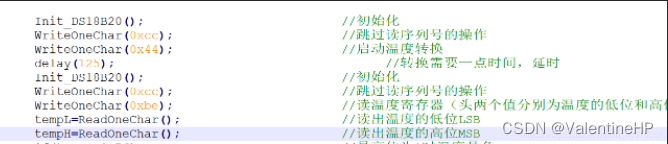

刚开始的时候,可以参考C51编写的代码来写Verilog的代码,这样可以很快的知道编写的流程是怎样的,以及状态机的状态有那些和一些注意事项

通过下面的C语言读取温度的过程,可以看知道读取温度的具体步骤

先启动温度转换,由于温度转换需要一点时间,所以需要一点等待,然后再进行读温度寄存器的命令,然后是读取温度了,最后通过上面的Figure2图进行装换。

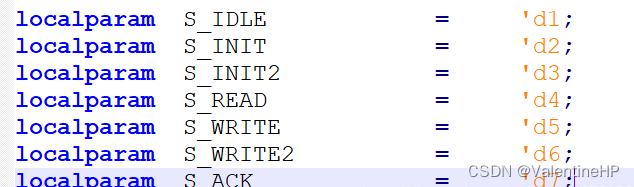

Verilog程序的状态机如下图,可以与上面的C程序很好的对应起来

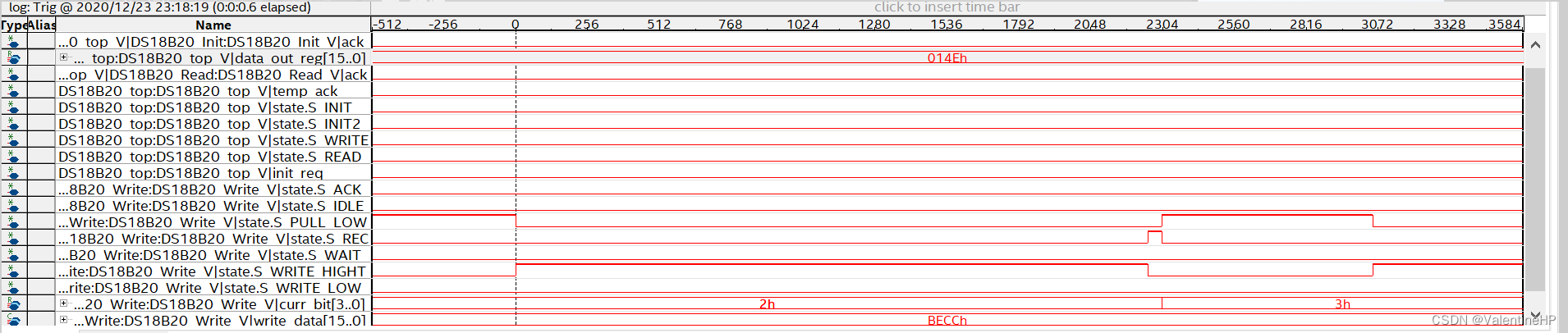

给出Signal Top抓取的信号图

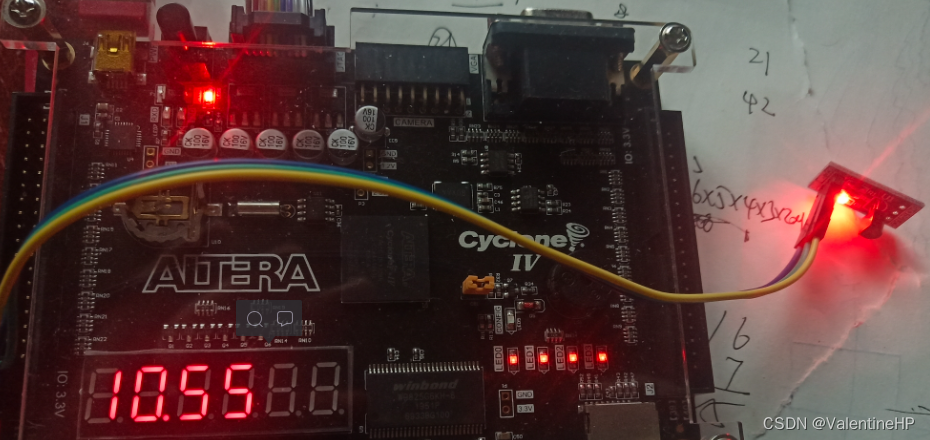

最后在开发板上的效果如下图

就不进行仿真了啦!

需要完整代码的可以在公众号中回复 :FPGA之旅设计99例之第八例

公众号:FPGA之旅