【FPGA】高云FPGA之科学的FPGA开发流程(一)https://developer.aliyun.com/article/1472626

4、功能仿真

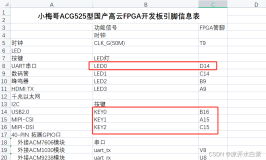

这里我们需要将我们的源代码设置为顶层文件(这里引用一下小梅哥的图),然后我们可以看到该源码所占用的资源情况

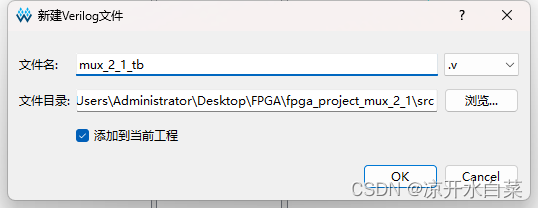

然后我们创建一个test beach测试文件

代码如下

`timescale 1ns/1ps module mux_2_1_tb(); reg In1; reg In2; reg Sel; wire Led; // 创建模块实例并赋值参数 mux_2_1 Mux_2_1( .in1(In1), .in2(In2), .sel(Sel), .led(Led) ); // 初始化运行 测试每个真值表上对应的参数设定 initial begin In1 = 0;In2 = 0;Sel = 0; #100; In1 = 0;In2 = 0;Sel = 1; #100; In1 = 0;In2 = 1;Sel = 0; #100; In1 = 0;In2 = 1;Sel = 1; #100; In1 = 1;In2 = 0;Sel = 0; #100; In1 = 1;In2 = 0;Sel = 1; #100; In1 = 1;In2 = 1;Sel = 0; #100; In1 = 1;In2 = 1;Sel = 1; #100; end endmodule

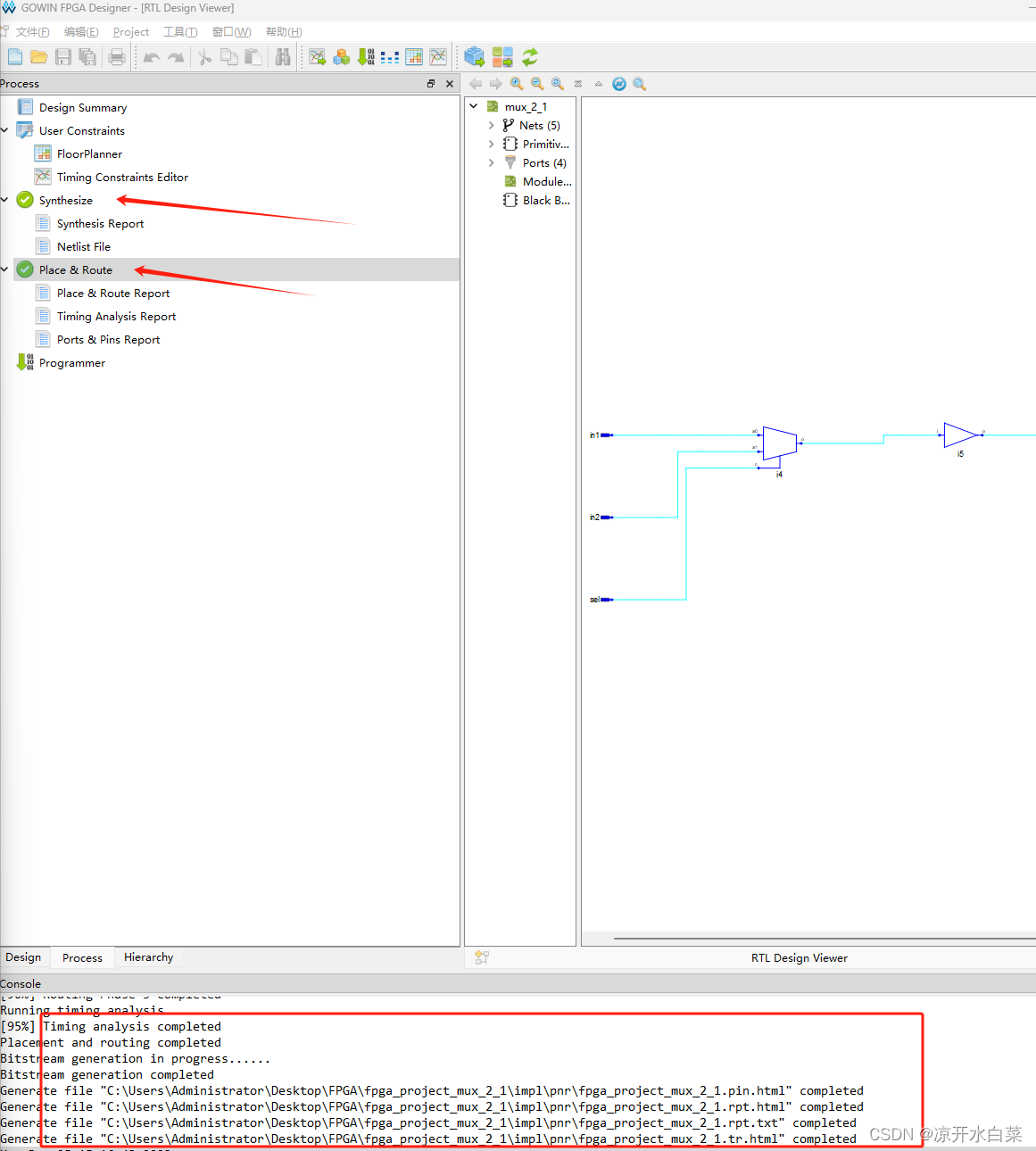

点击综合和布线,验证有无逻辑错误

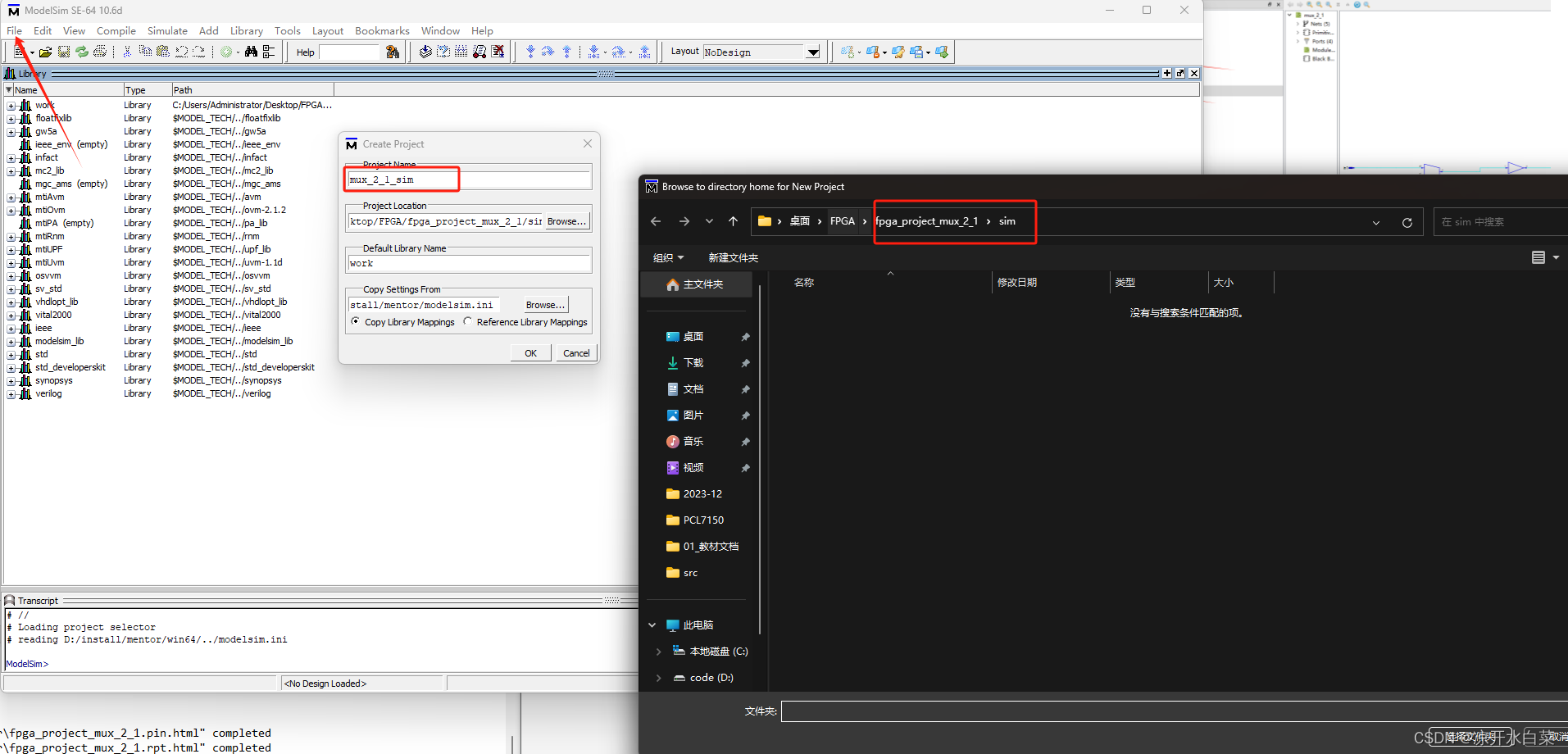

然后我们打开modsim软件创建工程

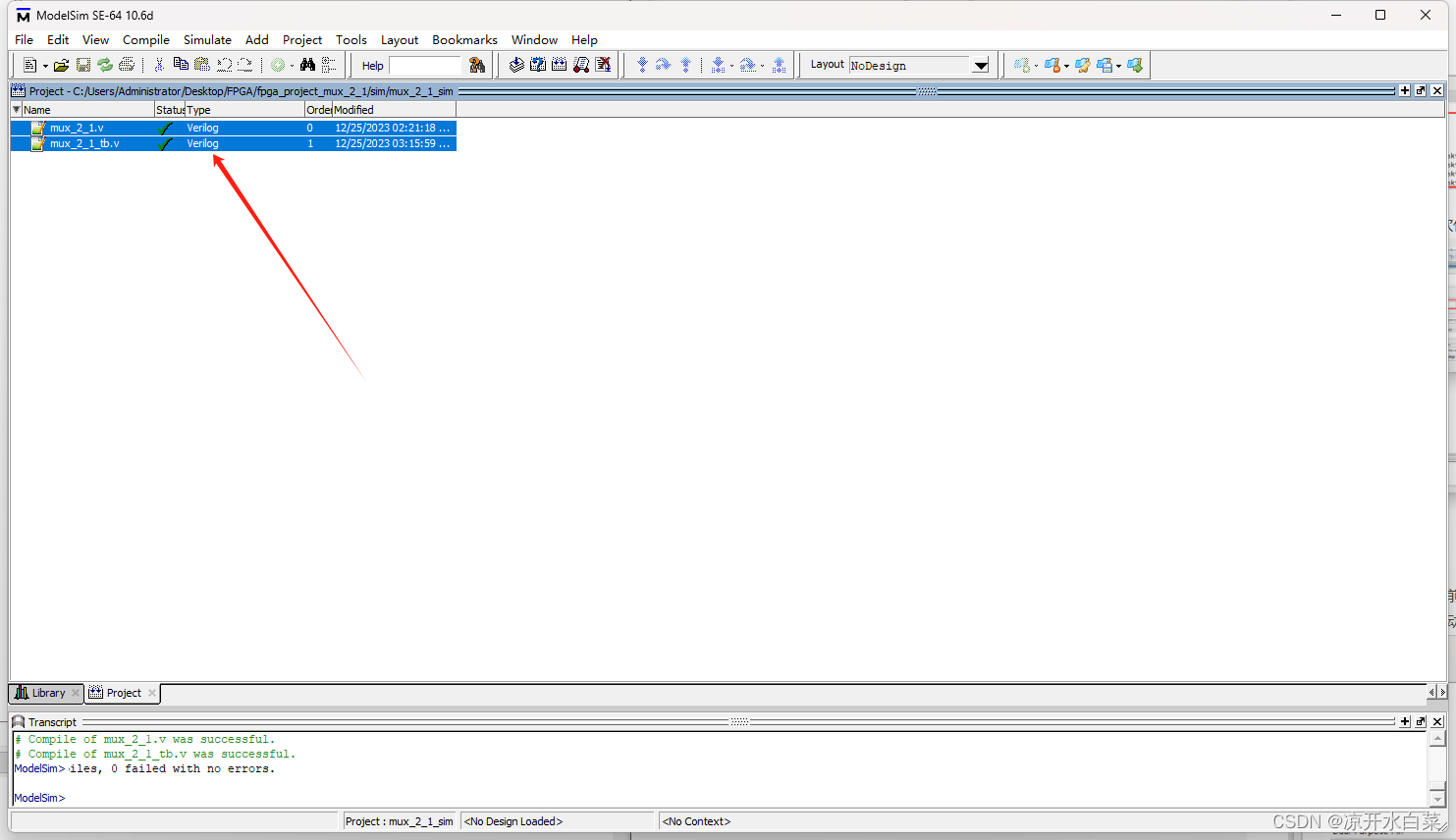

添加我们的两个源码文件并编译

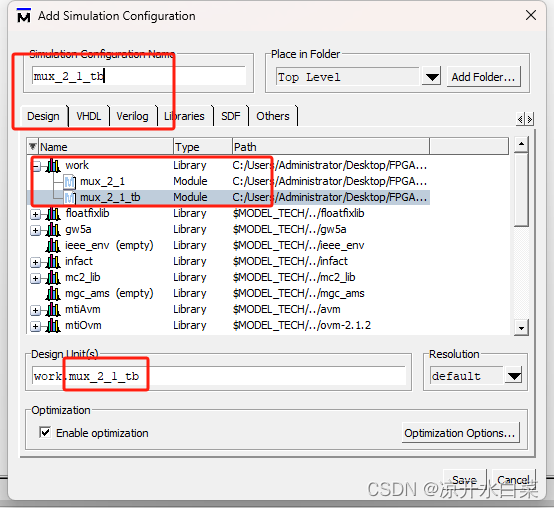

进入 Add Simulation Configuration 页面,我们在 Design 标签页面中选择work 库中的“ mux_2_1_tb”模块作为设计顶层,点击复制模块名作为仿真配置“ Simulation Configuration Name”的命名,确保命名保持一致。在复杂的工程设计中,我们可以设计多个不同的仿真配置顶层对工程进行仿真测试。

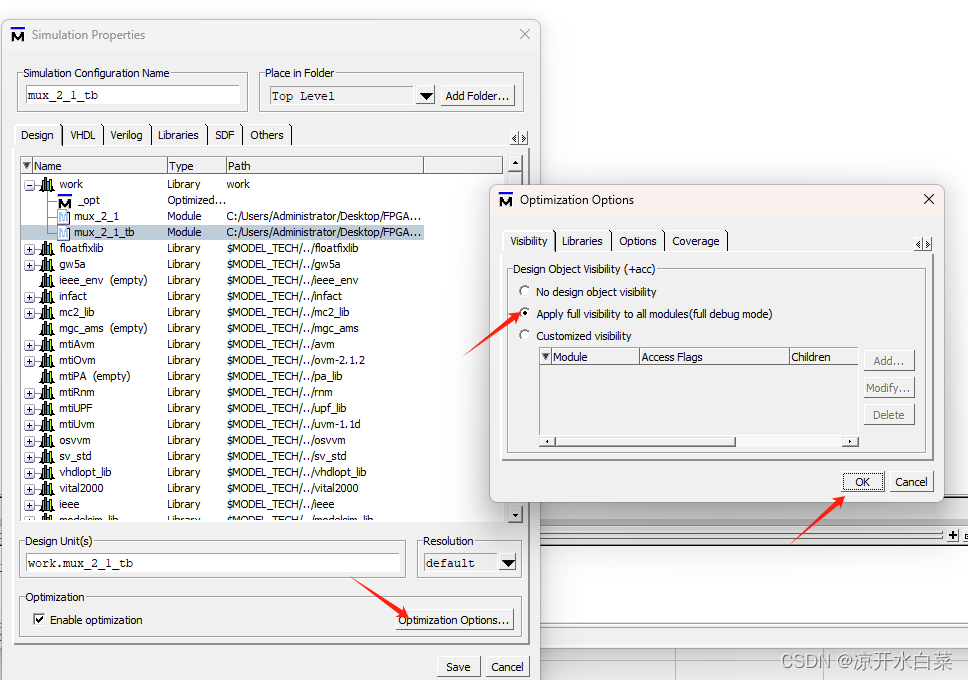

点击“ Optimization Options…”, 在“ Optimization Options…” 设置栏中选择“ Apply full visibility to all modules(full debug module)”,点击“ OK”

配置元件库(这一步的操作需要在modsim中已经添加了高云fpga的仿真库后操),点击“ libraries” 设置栏, 在“ Search libraries(-L)” 一栏中点击“ Add…”添加我们新建的高云的库文件“ gw5a”,在“ Search Libraries First(-Lf)”同样选择库文件“ gw5a”,最后点击“ Save”保存设置;

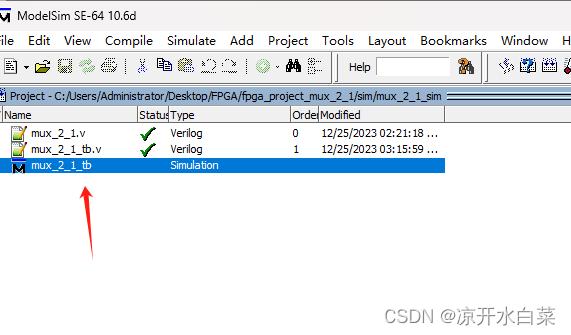

然后双击我们的仿真文件进入仿真界面

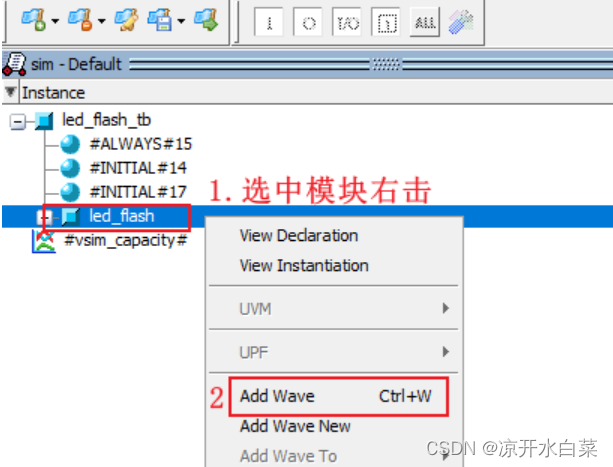

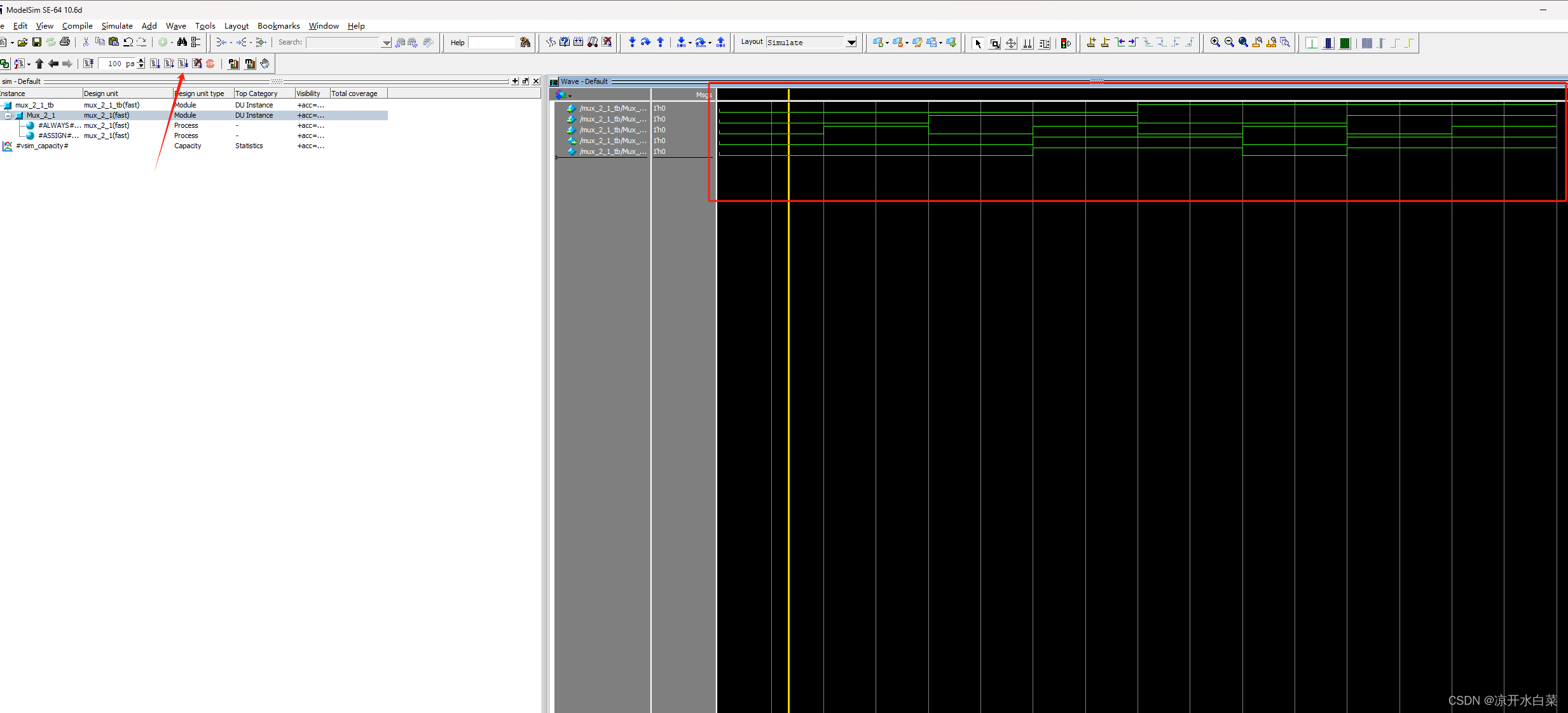

然后我们选中模块右击后点击Add Wave放到显示波形中

添加好波形后回到“ Library”栏,右键单击“ work”点击 Update 将

“ mux_2_1_tb”文件更新在“ work”栏,如下所示

然后我们点击状态栏中的运行即可捕捉到波形,然后右击Zoom Full可以快速查看波形,在这一步我们可以验证我们的波形是否是我们需要的效果;

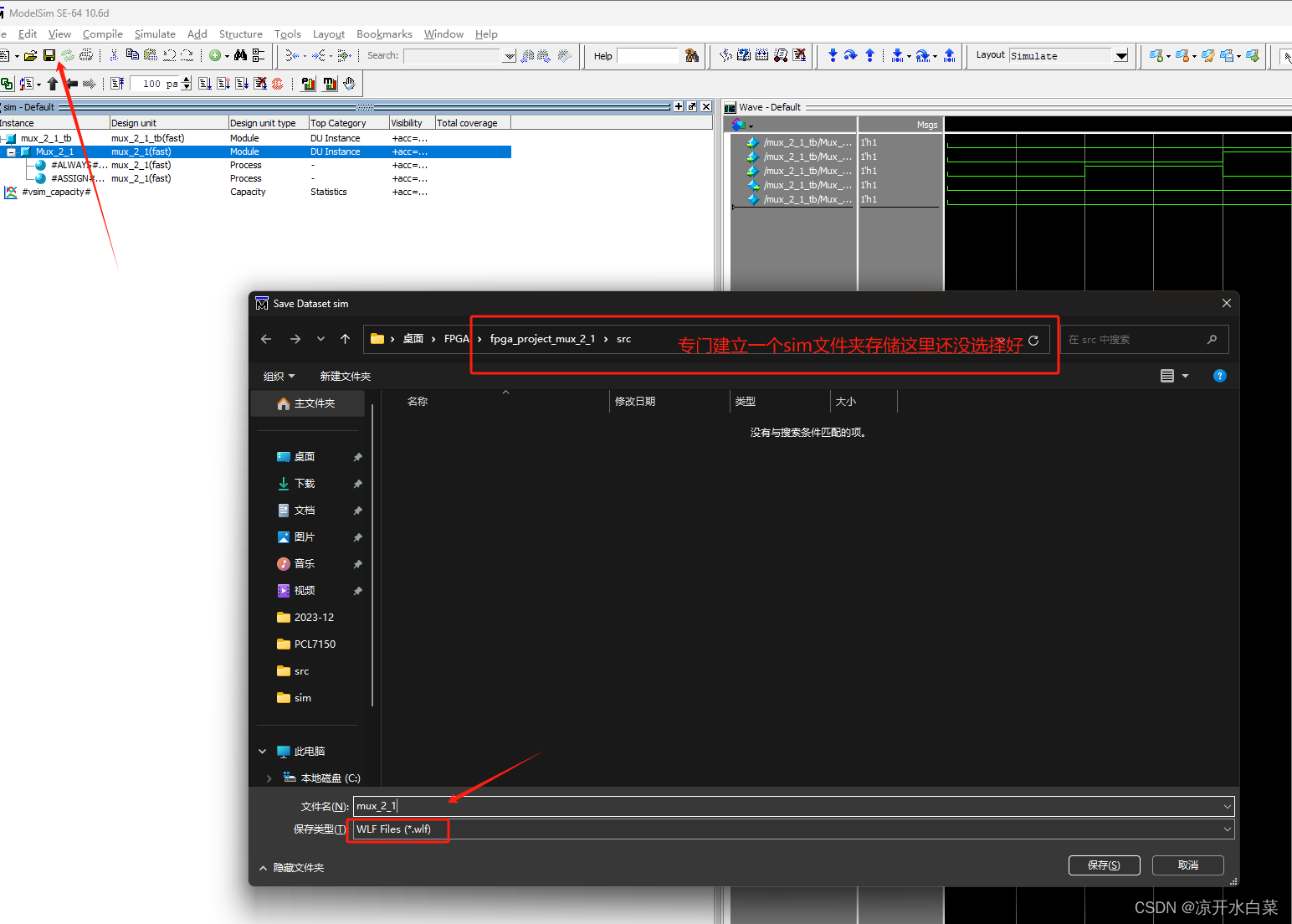

下一步我们可以将modsim的工程和波形文件保存到项目project路径下;

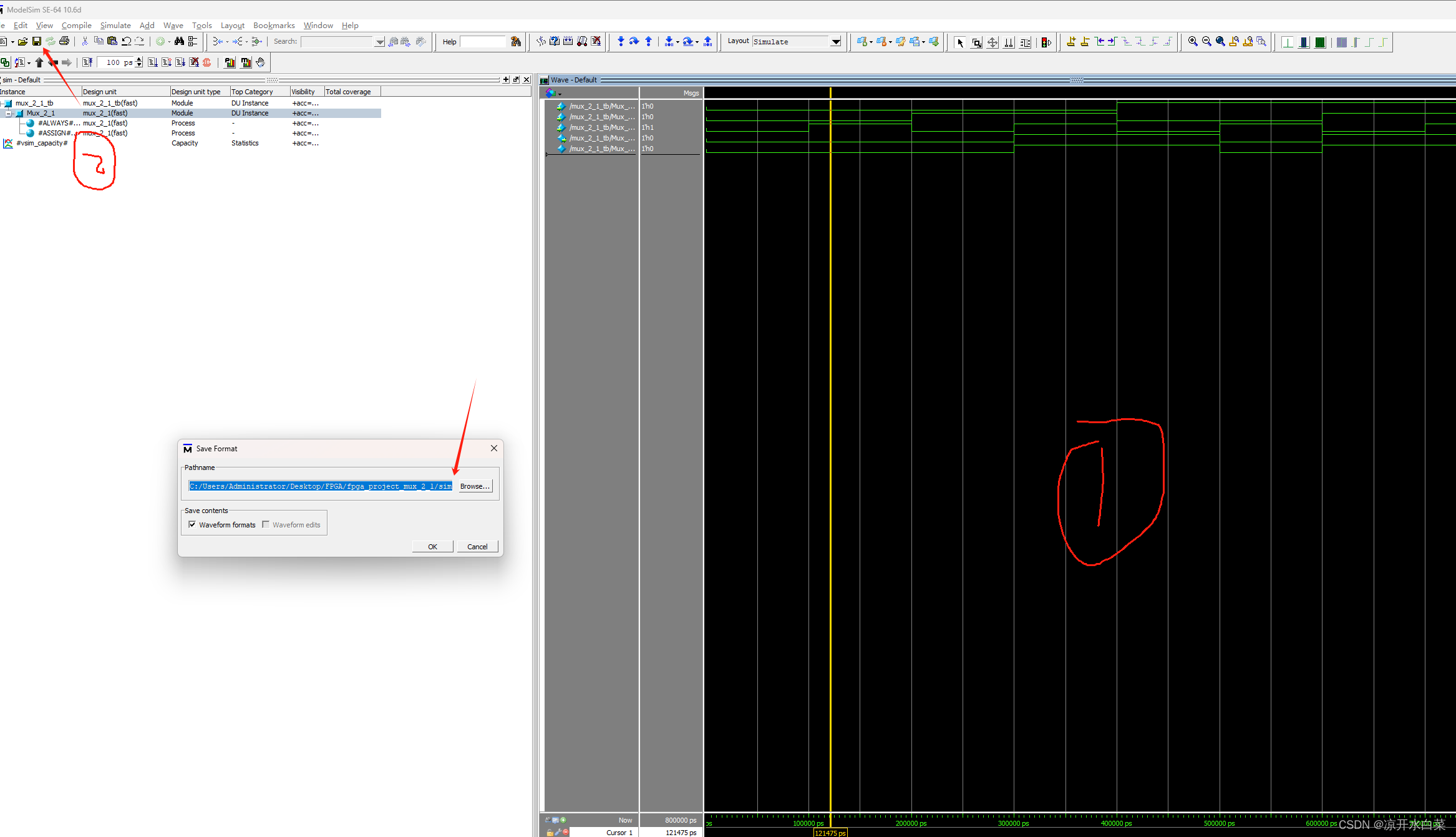

然后点击波形界面一下再点击这个按钮选择保存波形路径

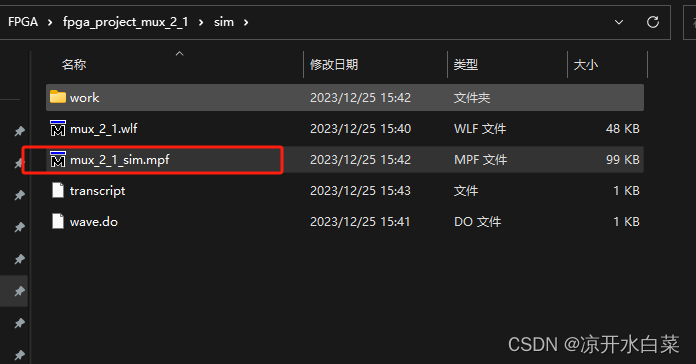

下次还需打开工程只需要点击该目录下的.mpf文件即可

到这里功能仿真也就是RTL仿真就结束了,下一步我们需要分配我们程序中引脚并完成布局布线;

【FPGA】高云FPGA之科学的FPGA开发流程(三)https://developer.aliyun.com/article/1472628