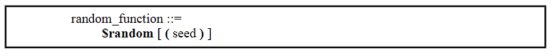

$random系统函数语法的BNF范式如下所示,有关BNF范式相关内容,可以浏览以往文章Verilog基础:巴科斯范式(BNF)。

$random系统函数在每次调用时返回一个32位的随机数,这个随机数是有符号的,可正可负。按照Verilog标准语法,$random系统函数的调用方式为$random或$random(seed),但实际上$random()这种调用方式也是可以的,且其与$random完全一样。

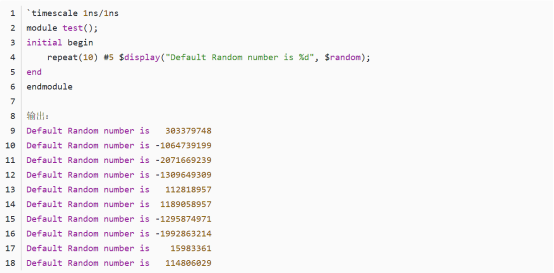

seed是系统函数产生随机数的种子,当不指定种子时,如$random()或$random,系统会默认指定一个在每次调用后都会改变的隐形种子,且种子的改变轨迹是确定的,具体如下所示。

上面代码的随机数序列是确定的,即第一次调用系统函数时返回303379748,第二次时返回-1064739199,以此类推。

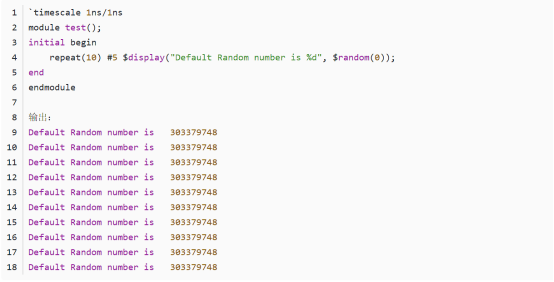

对于相同数值的种子,系统函数会返回相同的值,如下所示。

从上面的输出我们还可以发现,系统默认的隐形种子的种子值可能就是从0开始。

如果指定了种子值,我们必须保证在每次调用系统函数前的种子值是不同的,这样才能得到一个看近似随机的数字,如使用$time系统函数,它会返回当前的仿真时间。

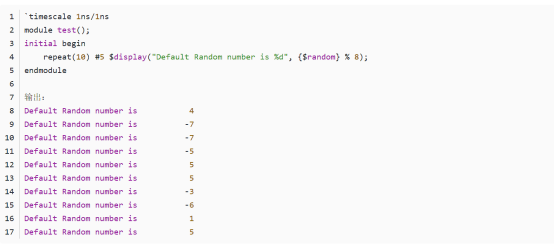

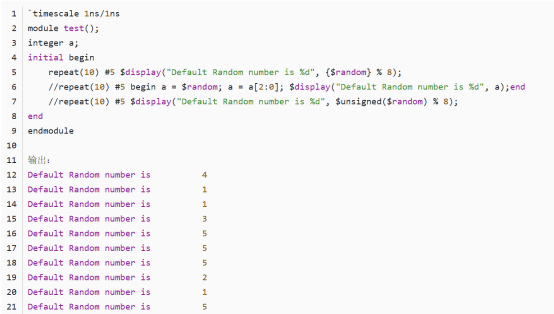

$random系统函数返回的是32位有符号数,如果我们不需要这么大的有符号数可以使用求余运算符得到一个小的随机数,如下所示。

通过对8求余,我们得到了一个位于-7到7之间的随机数。

如果我们需要无符号的随机数,我们可以利用拼接运算符、域选或$unsigned系统函数,如下所示。

三种方法的输出结果是一样的,因为他们的原理是类似的,{}拼接运算符的结果是无符号的;域选运算符的结果也是无符号的,同时域选的位宽还可以保证输出数据的大小,这甚至省略了求余的操作;$unsigned系统函数可以直接将一个有符号数转换为无符号数。