一. 简介

由于项目需要使用到eMMC存储器,所以特地的去学习了一下。在网上也找了许多资料,但大多是介绍性的,以及对文档的翻译,没能很好的讲解如何从零编写Verilog代码来控制eMMC。看了很多文章,但大多大同小异,还是无从下手。

故在这里分享我的学习例程,教大家如何编写eMMC驱动,以使用为主,至于一些理论和不相关就不作介绍了,同时可以作为参考,避免踩坑,同时欢迎大家与我交流,共同进步。

本例基于JESD84-B50手册进行学习,也就是eMMC5.0,目前最新的好像是eMMC5.1,但差距应该不大。该版本支持高速,HS200和HS400。

最终实现 驱动 支持 高速,HS200和HS400三种模式

需要手册可以关注 FPGA之旅 回复 JESD84-B50手册 获取

回复eMMC代码V1 获取完整工程,目前支持高速和HS200.HS400有点问题,可能是我PCB的问题。

下面就是进入正题吧!

FPGA驱动eMMC系列(二)-------上电初始化

二. eMMC主要功能介绍

(1) eMMC接口

ps: 图例都来原图文档

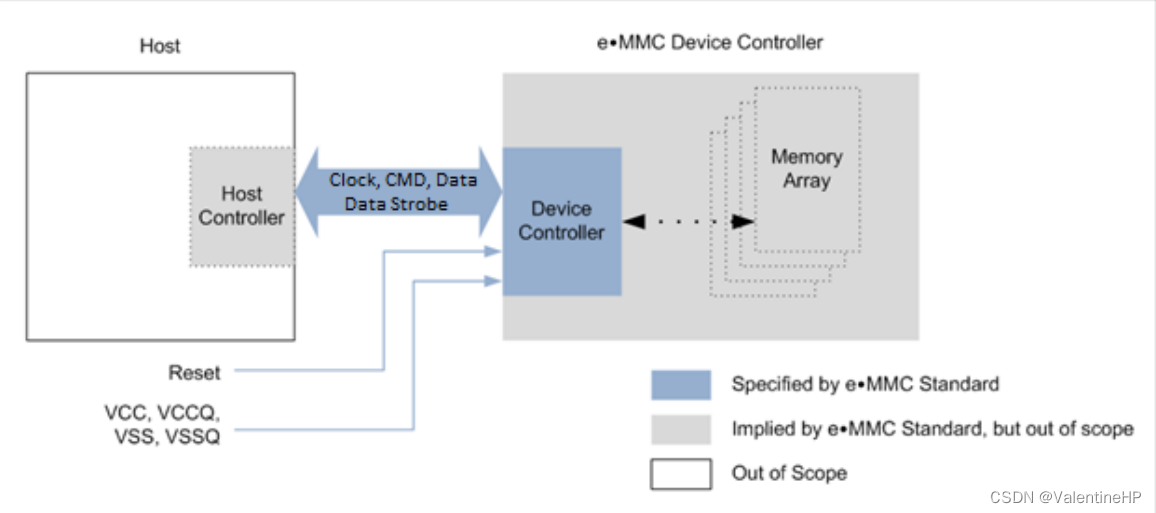

通过下图可以看到,FPGA和eMMC通信只需要四种信号即可。可以看到接口是如此的简单。

Clock (1bit):时钟,FPGA输入给eMMC的时钟

CMD (1bit ) :inout类型,用于FPGA向eMMC发送命令,以及eMMC向FPGA返回响应

Data (1bit 4bit 8bit) : inout类型,用于向eMMC写入数据和读出数据,可以配置为1/4/8bit三种

Data Strobe (1bit) :eMMC输入给FPGA的时钟,只有在HS400模式中有效(读数据的时候以及写数据后的响应)

(2) 命令发送过程

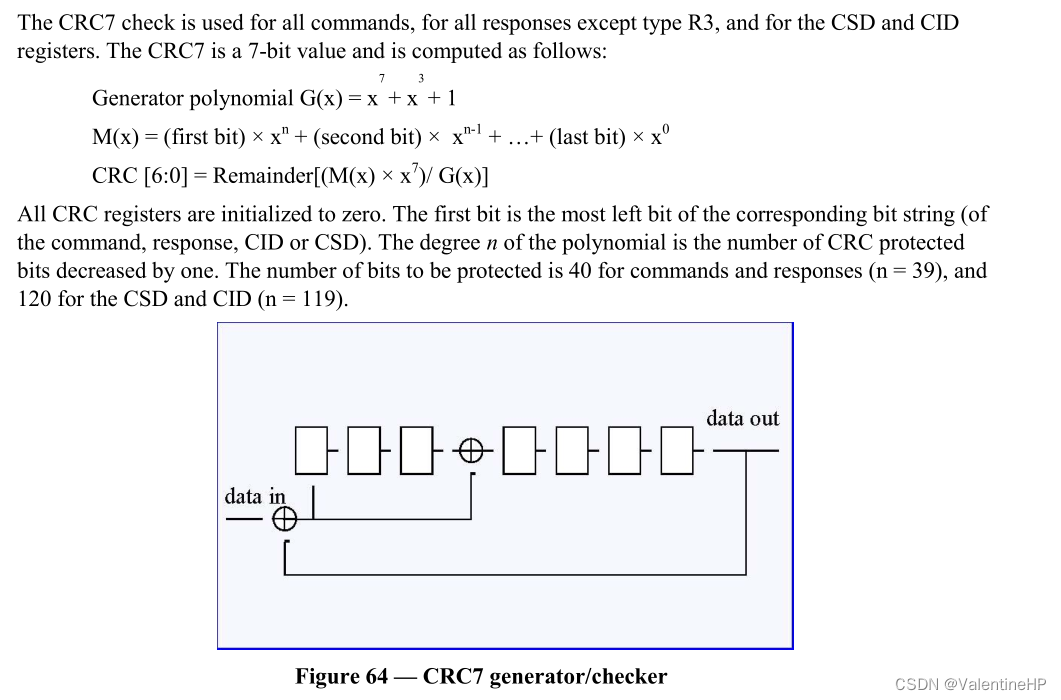

eMMC中,命令的长度固定为48bit,格式如下,其中Content根据不同的命令写入不同的数值,CRC校验数据包括 Start bit ,Transmitter bit 以及 Content,CRC多项式后面稍后再说。

每发送一个命令(广播类型的命令除外),eMMC都会返回一个响应,响应有两种不同的数据长度,分别为48bit和136bit。具体表示什么意思,暂不纠结。

(3) 数据传输过程

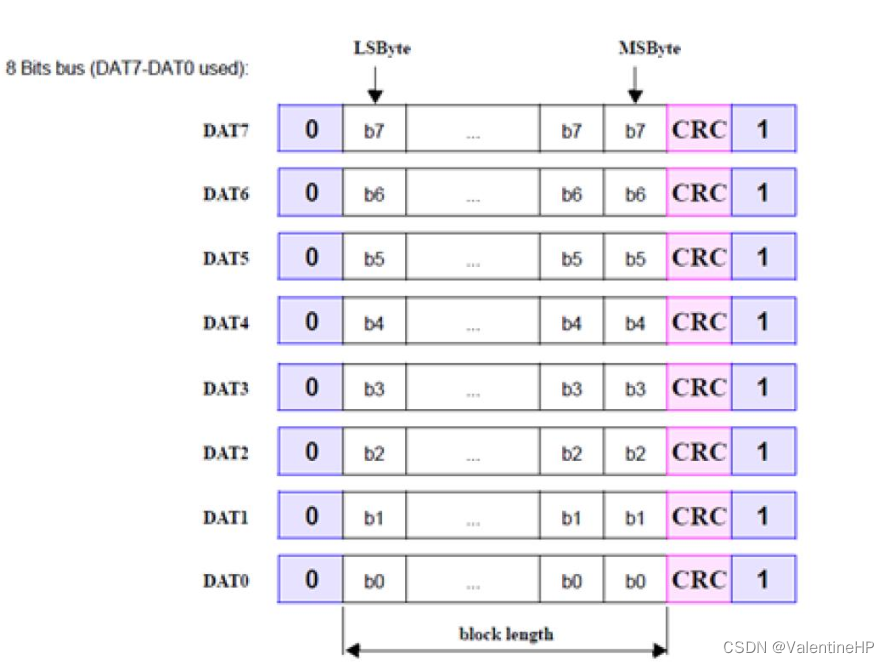

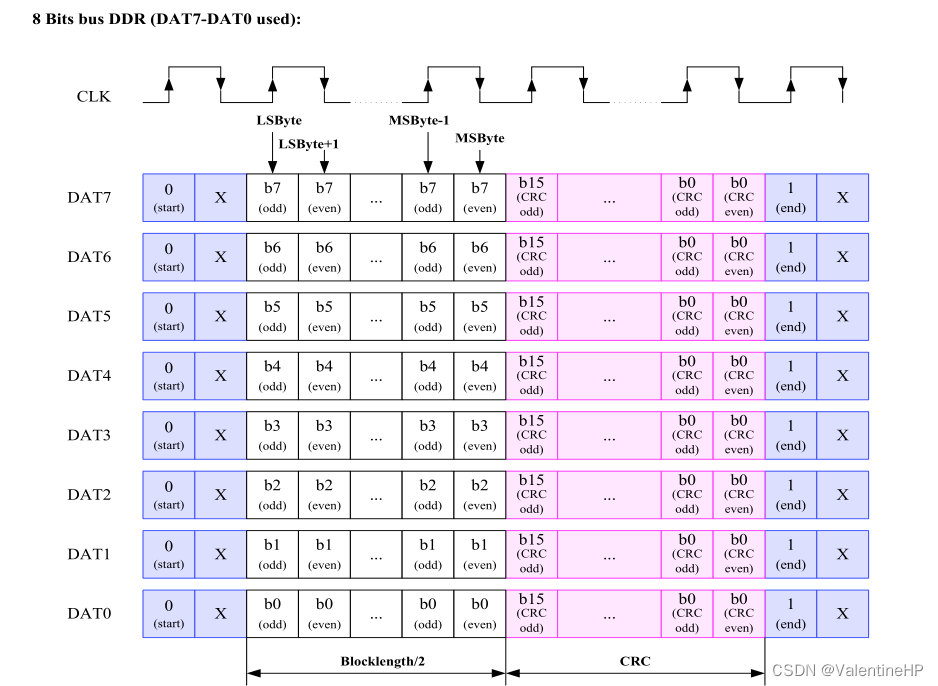

以8 bit的模式说明,也是用到最多的一种,毕竟快嘛。数据传输过程包括两种模式SDR和DDR,时钟单边沿出数据,和双边沿出数据。

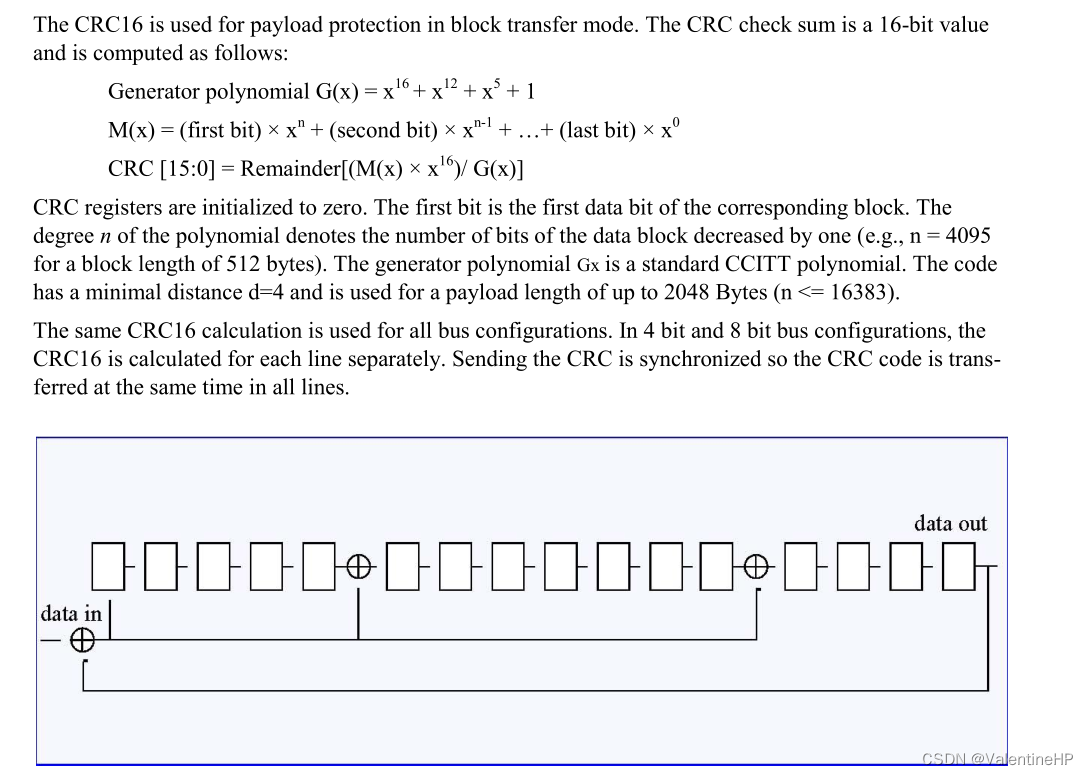

SDR模式如下,传输格式 为 :起始位 + 数据 + CRC校验(CRC16) + 停止位。其中block length可以自己配置,默认为512。这里的CRC只包括数据,不包括起始位了。

DDR 模式如下,可以看到,在时钟的上下边沿,都有数据输出,注意这里的block length只能配置为512,其他的大小不支持。需要对上边沿的数据 和 下边沿的数据 分别计算CRC,然后再输出。

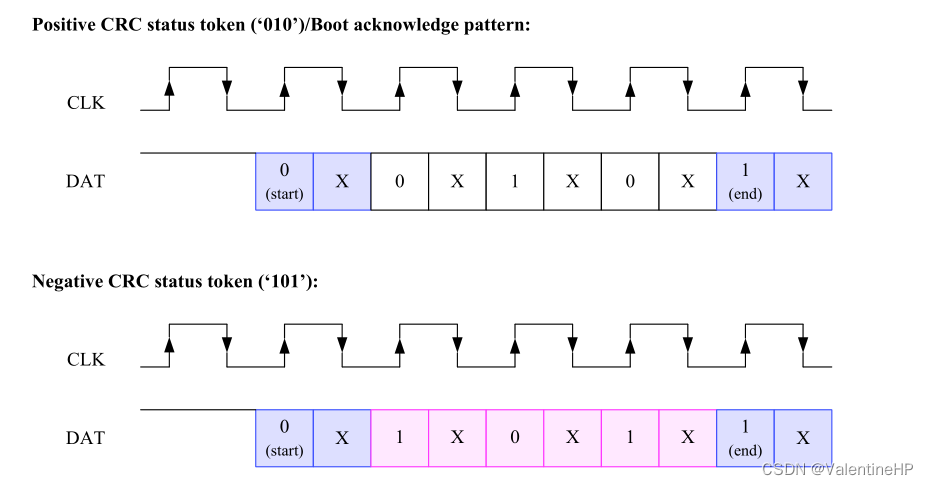

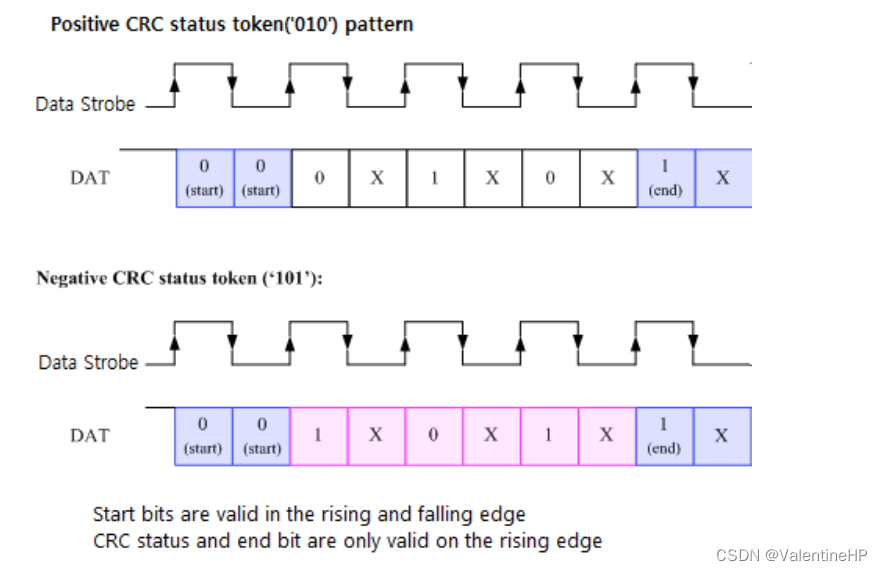

另外,在向eMMC写数据的时候,每一帧数据完成后,eMMC会在DAT0上向FPGA放回一个CRC校验,表示是否成功接收到数据。通过这个CRC判断是否成功写入。

如果接收成功,那么就会接收到Positive CRC(010), 失败的话,则会接收到 Negative CRC(101)

SDR

DDR

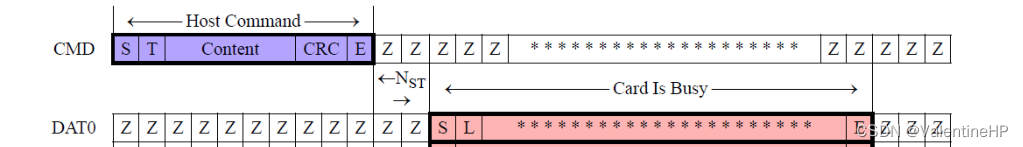

(4) eMMC设备忙

在发送命令后,或者写入数据后,设备不能立马完成对应的工作,这时候,eMMC会拉低DAT0,表示busy,参考图如下。

(5)CRC校验

eMMC中只包括两种CRC校验多项式,分别是命令的CRC7和数据的CRC16。具体形式如下,后面再介绍如何具体实现。

到这里,就将eMMC的接口时序详细的说明了一下。更多细节,将在后面一一说明。

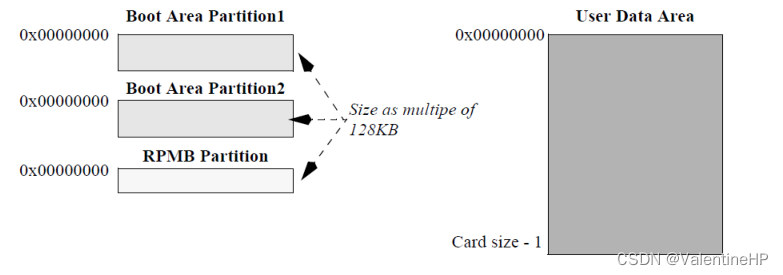

(5) eMMC存储区域

eMMC内部有三种存储区域,我们使用的是User Data Area区域,其他两种不作介绍。

三 小结

通过这部分的学习,大体对eMMC有了一个初步的了解。对命令和数据的传输过程有了具体的认识。也达到了本篇文章的目的。

下篇,将介绍如何进行上电 初始化。

公众号:FPGA之旅