一. 简介

本例是FPGA之旅设计的第十四例,本例将红外遥控的使用,并将红外接收器接收到红外遥控的数据显示在数码管上。

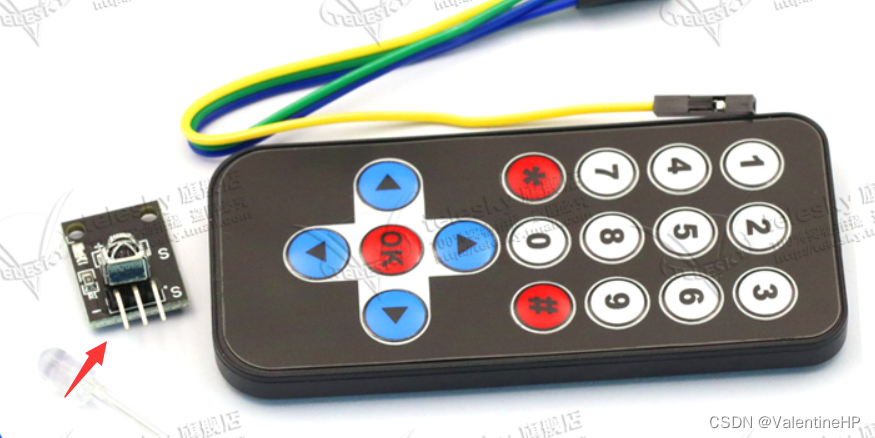

红外遥控接收器模块,非常简单,也是由GND,VCC和数据三个引脚组成,通过杜邦线可以直接连接在FPGA的IO口上,产品细节如下。

二. 红外数据传输

数据传输过程如下

引导码:标志的数据传输的开始。

数据码:传输红外遥控发送的数据,一帧数据共有32bit,4个字节。分别为地址,地址反码,数据,数据反码。先发送低位。

停止码:标志着数据传输的完成。

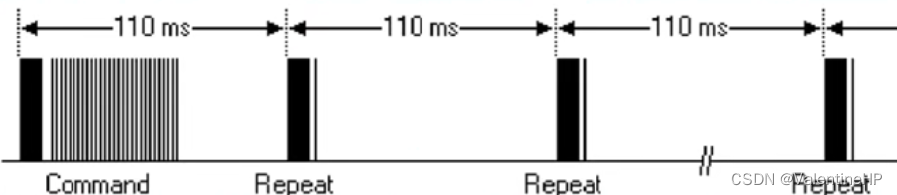

重复码:当一直按下某个按键的时候,并不会再次发送数据,而且通过重复码标志按键一直处于按下的状态。如果一直按下的话,约110ms,发送一次重复码。

在对数据传输过程有了个大致的了解后,下面就对每个部分进行详细的讲解。

所有波形都是对于遥控器来说的

(一). 引导码

引导码波形如下,遥控器先发送9ms的信号,然后空闲4.5ms后,引导码结束。

这个时候在开发板上结束到的电平变化为,9ms的低电平,4.5ms的高电平。也就是说,遥控器发送信号的时候,接收器上为低电平,遥控器空闲时,接收器上为高电平,这点在处理的时候需要注意。

(二). 数据码

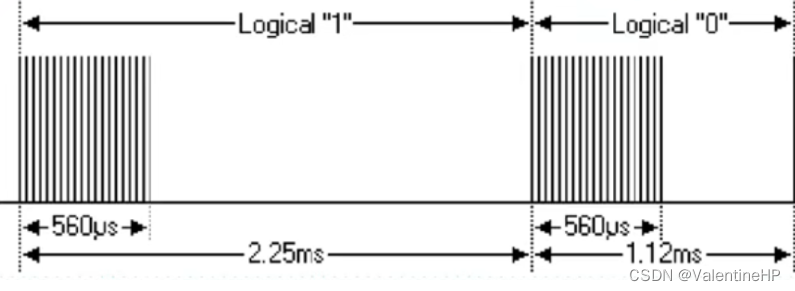

数据码主要是看,数据0和数据1是如何表示的。通过下图可知,**数据1是560us的信号,加1.69ms的空闲。数据0是560us的信号,加560us的空闲。**知道了数据是如何表示的后,在接收的时候,只需要按照波形接收32bit的数据即可。

(三). 结束码

在最后一个数据接收完成了,遥控器会发送560us的信号,然后空闲,表示发送结束。

(四). 重复码

重复码,是和引导码对应的,如果发送的是重复码的话,引导码中的空闲4.5ms,会变成2.25ms,然后直接进入结束吗。根据空闲时间的长短,可以判断是引导码,还是重复码。

了解了其发送的波形变换情况,就可以进行代码的编写了。

三. Verilog代码实现

(一). 端口信号确定

端口信号很简洁,当接到一次红外数据的时候,infrared_end,就会拉高一个周期。

Infrared_Reception( input sys_clk, input rst_n, input infrared, //红外信号IO output infrared_end, //接收数据完成 output[7:0] infrared_data //接收到的数据 );

(二). 状态确定

通过上面的分析可知,一共可以分为如下四个状态。I_START其中包括引导码和重复码,根据时间可以确定,下一个状态该跳转到那。

localparam I_IDLE = 'd0; //空闲态 localparam I_START = 'd1; //开始态,也就是引导码阶段 localparam I_DATA = 'd2; //数据态 localparam I_END = 'd3; //结束态

(三). 状态机跳转

always@(*) begin case(state) I_IDLE: if(infrared_negedge == 1'b1) next_state <= I_START; else next_state <= I_IDLE; I_START: if(infrared_negedge == 1'b1) if(time_cnt < Infrared_Time2_25ms) //表示重复码,直接放回上一次的接收值 next_state <= I_END; else next_state <= I_DATA; else next_state <= I_START; I_DATA: if(infrecv_bit_cnt == 'd31 && infrared_negedge == 1'b1) next_state <= I_END; else next_state <= I_DATA; I_END: if(infrared_posedge == 1'b1) next_state <= I_IDLE; else next_state <= I_END; default: next_state <= I_IDLE; endcase end

效果图如下。

需要完整代码的可以发送 FPGA之旅设计99例之第十四例 获取

公众号:FPGA之旅