一. 简介

这是FPGA之旅的第十一例了。在前面的例子中,已经对OLED有了一个基础的了解,本例将介绍如何在OLED上实现支符的显示,为后面的例程做准备。

显示字符需要先使用字摸软件取模,将得到的字摸数据存储到寄存器当中,这个过程可以利用Python生成。然后设置好显示的XY坐标,最后发送字符数据即可。对于字符占两个page的话,也就是字符高度大于8的情况,中间还需要重新设置page。

二. 字摸软件简介

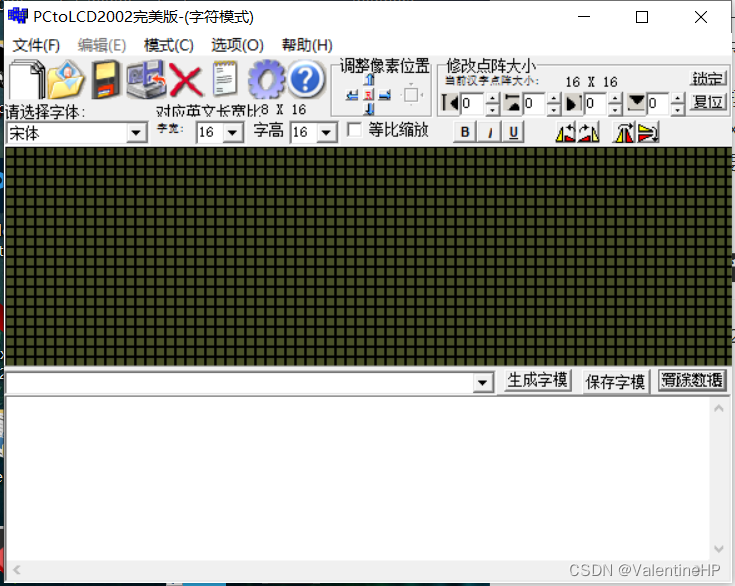

字摸软件选用PCtoLCD2002,这个比较常用,也是比较方便,界面如下图所示。

点击选项,在弹出的界面中,对生成的字符数据进行设置,为了方便python进行解析,特意设置生成格式如下。

设置好后,×掉,设置好字宽和字高后,输入需要生成的字符数据,然后点击生成字摸就可以在文本框中看到生成的数据,然后点击保存字摸,就可以将字摸数据保存到TXT文件中了。字摸软件的介绍就到这里了。

三. Python程序编写

想着,大家对python可能不太了解,程序就不贴出来,可以作为一个工具来用,对每个字符生成如下的always块,字体大小为16*16,方便FPGA读取。

always@(posedge clk or negedge rst) begin if(rst == 1'b0) begin data1[0] = 8'h00; data1[1] = 8'h40; data1[2] = 8'h64; data1[3] = 8'h1C; data1[4] = 8'h8A; data1[5] = 8'h6C; data1[6] = 8'h1C; data1[7] = 8'h04; data1[8] = 8'hFC; data1[9] = 8'h8A; data1[10] = 8'h5C; data1[11] = 8'h64; data1[12] = 8'h54; data1[13] = 8'h54; data1[14] = 8'h10; data1[15] = 8'h00; end end

四. 字符显示模块

这里演示的是8*16大小的字符(中途没有换行操作,便于理解显示的过程),也就是显示一个字符,需要向OLED发送16次IIC请求。

(一) 模块信号列表

现在这个模块和初始化模块一样,信号列表都是一样的。当字符请求来了,就把显示的字符数据发送出去。

module OLED_ShowFont( input sys_clk, input rst_n, input ShowFont_req, //字符显示请求 input write_done, //iic一组数据写完成 output[23:0] ShowFont_Data, //字符显示数据 output ShowFont_finish //字符显示完成 );

(二). 具体代码实现

显示一个8*16大小的字符,需要先指定对应的XY坐标,也就是page数和Column地址,发送三个命令即可。

随后发送16byte的字符数据,就完成了一个支符的显示。

always@(*) begin case(showfont_index) 'd0 showfont_data_reg <= {8'h78,8'h00,8'hB0 + 8'h03}; //'d3代表显示的起始页地址为4 'd1: showfont_data_reg <= {8'h78,8'h00,8'h00 + 8'h02}; //'d2代表显示的起始column的低四位为2 'd2: showfont_data_reg <= {8'h78,8'h00,8'h10 + 8'h02}; //'d2代表显示的起始column的高四位为2 //即显示的column的起始地址为8'h22,即'd34 default: showfont_data_reg <= {8'h78,8'h40,fontdata};//显示的数据 endcase end OLED_FontData OLED_FontData_HP( .sys_clk (sys_clk), .rst_n (rst_n), .index (showfont_index - 'd3), .data (fontdata) );

发送完3byte+16byte的数据后,即显示结束,也就是当showfont_index == 18的时候,并且在第19个数据刚刚写完的时候。

assign showFont_finish = (showfont_index == 'd18 && write_done == 1'b1) ? 1'b1 : 1'b0; always@(posedge sys_clk or negedge rst_n) begin if(rst_n == 1'b0) showfont_index <= 'd0; else if(showFont_finish == 1'b1) //字符数据显示完后,showfont_index置0 showfont_index <= 'd0; else if(write_done == 1'b1) //每写完一组数据,showfont_index就加一 showfont_index <= showfont_index + 1'b1; else showfont_index <= showfont_index; end

(三). OLED_TOP模块改动

这部分的修改也很少,只需要添加一个状态,在OLED初始化完成后,进入字符显示状态,最后进入空闲态即可,其他的添加和初始化部分一样。

always@(*) begin case(state) OLED_INIT: if(init_finish == 1'b1) next_state <= OLED_ShowFont; else next_state <= OLED_INIT; OLED_ShowFont: if(showfont_finish == 1'b1) next_state <= OLED_IDLE; else next_state <= OLED_ShowFont; OLED_IDLE: next_state <= OLED_IDLE; default: next_state <= OLED_INIT; endcase end

这里就进行了一个简单的字符显示例程,当然在实际使用的时候,会复杂很多,例如有多个不同大小的字符进行显示,以及动态显示字符等等情况,但核心的写法可以参考本例。

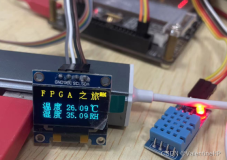

显示效果如下

微信公众号回复 FPGA之旅设计99例之第十一例 获取工程文件

公众号:FPGA之旅