一. 简介

在学习了前面几例之后,就可以做一个小设计啦,本次分享的是数字时钟,也是在课设中经常出现的题目,虽然难度系数系数不大,但可以很好的锻炼一下综合能力,特别是对于刚刚接触FPGA的小伙伴来说。

演示视频.

二. 所需硬件

所使用到的硬件极少,一般开发板上都带了。

六个动态数码管 : 用来显示时间

按键 :用来控制

三. 功能介绍

时-分-秒显示,为24小时制

通过按键可以动态调整时间

通过按键可以动态选择要调整的时间,对应的数码管闪烁

按键消抖

将前面的几个案例都结和起来了(没有包括uart和iic)。

四. 核心代码介绍

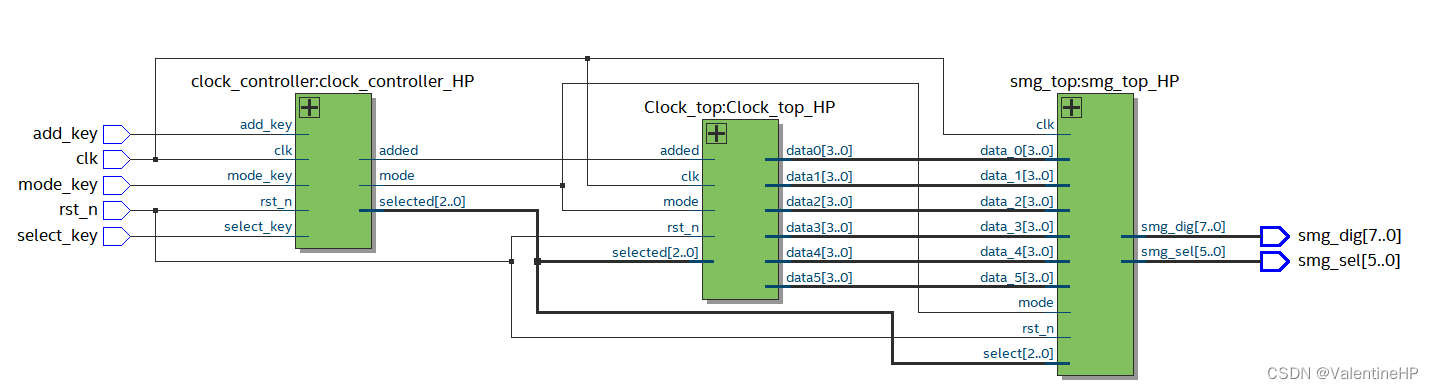

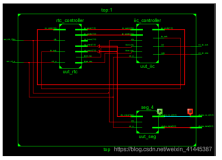

1.RTL图

本代码项目一共由三个模块核心模块组成

时钟控制模块 : 通过接收外部按键的输入,来设置当前项目的显示模式

时钟模块 : 生成时分秒三个数据

数码管显示模块: 接收时钟模块提供的数据,驱动数码管的显示

2.数码管选中闪烁

twinkle_en为亮或者暗使能信号,select是否选择当前数码管

通过代码可以看到twinkle_en为1的时候,并且select选中了当前数码管的时候,数码管为暗,其他时候都为亮。

这样当select不变的情况下,通过修改twinkle_en切换的频率,就可以实现数码管选中闪烁的例子了。

if( twinkle_en == 1'b0) smg_sel_reg <= 6'b111_110; else if( twinkle_en == 1'b1 && select == 'd0) smg_sel_reg <= 6'b111_111; else smg_sel_reg <=6'b111_110;

分离时分秒数据

时分秒每个数据都需要用到两个数码管进行显示,这样就需要分离出数据的高位和地位,通过如下方法可以快速获取。

assign data0 = sec_data %10; //地位 assign data1 = (sec_data > 'd49) ? 'd5 : (sec_data > 'd39) ?'d4 : (sec_data > 'd29) ?'d3 : (sec_data > 'd19) ? 'd2: (sec_data > 'd9) ? 'd1 :'d0; //高位 //方法二,获取高位 assign data1 = ((sec_data - data0 )/10)%10;

至此核心代码就介绍完成了。

需要可以gzh回复 FPGA之旅设计99例之第七例 获取下载链接

公众号:FPGA之旅