前言

本文节选UG471的第二章,进行整理翻译,用于介绍SelectIO资源内部的ODELAY资源。

ODELAY资源简介

输出延迟资源 (ODELAY) 在HR Bank 中不可用。每个 HP I/O 模块都包含一个称为 ODELAYE2 的可编程绝对延迟原语。ODELAY 可以连接到 OLOGICE2/OSERDESE2 块。 ODELAY 是一个 31 抽头、环绕式延迟原语,具有校准的抽头分辨率。 延迟值参阅 7 系列 FPGA 数据手册。 它可以应用于组合输出路径或注册输出路径。 它也可以直接从 FPGA 逻辑访问。 ODELAY 允许单独延迟输出信号。 通过从 7 系列 FPGA 数据手册中指定的范围中选择一个 IDELAYCTRL 参考时钟来改变抽头延迟分辨率。

ODELAYE2 原语

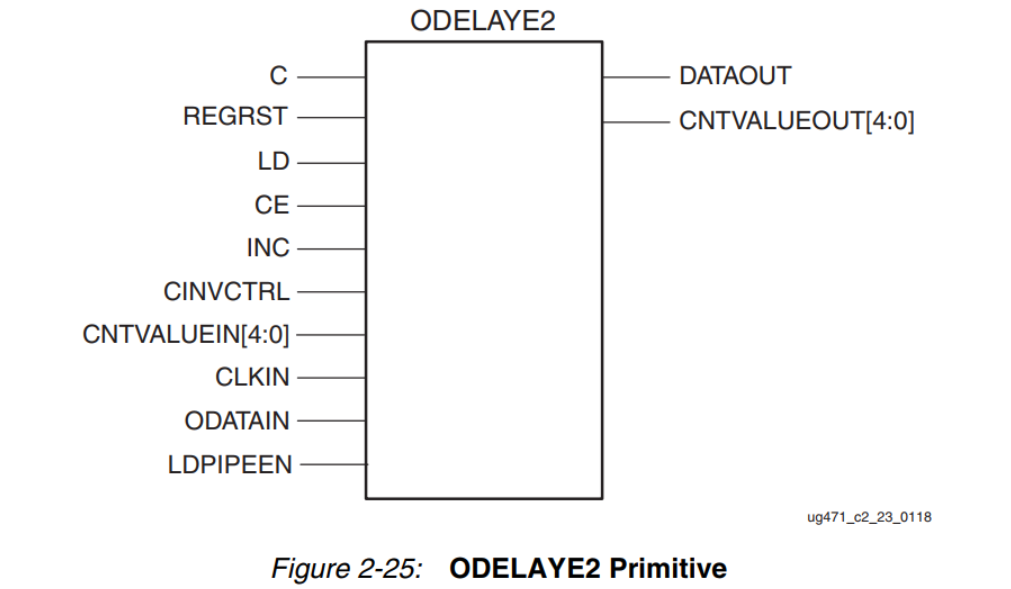

下图显示了 ODELAYE2 原语。

ODELAYE2 端口

端口概述表如下:

端口介绍

来自 FPGA OLOGICE2/OSERDESE2 的数据输入 - ODATAIN

ODATAIN 输入由 OLOGICE2/OSERDESE2 驱动。 ODATAIN 驱动连接到 IOB 的 DATAOUT 端口,延迟由 ODELAY_VALUE 设置。

来自时钟缓冲器的时钟输入 - CLKIN

CLKIN 输入由时钟缓冲器(BUFIO、BUFG 或 BUFR)驱动。 然后,此时钟会延迟一个设置为 ODELAY_VALUE 的值,并通过 DATAOUT 和输出缓冲区(OBUFT 或 OBUFTDS)输出。 当使用 IOBUF 时,延迟的时钟可以路由回 FPGA 逻辑。当使用 IOBUF 将时钟路由回 FPGA 时,会使用 FPGA 的封装引脚。

数据输出 - DATAOUT

来自两个数据输入端口之一的延迟数据。 DATAOUT 连接到 IOB。

时钟输入 - C

ODELAYE2 原语(LD、CE 和 INC)的所有控制输入与时钟输入 © 同步。 当 ODELAY 配置为 VARIABLE、VAR_LOAD 或 VAR_LOAD_PIPE 模式时,必须将时钟连接到此端口。 C 可以局部反转,并且必须由全局或区域时钟缓冲器提供。 该时钟必须连接到与 SelectIO 逻辑资源中使用的时钟相同的时钟。 例如,当使用 OSERDESE2 时,C 连接到与 CLKDIV 相同的时钟。 如果 IDELAYE2 原语与 ODELAYE2 原语在同一个 I/O bank 中使用,C 必须为这两个原语使用相同的时钟网络。

模块加载 - LD

在 VARIABLE 模式下,ODELAY 加载端口 LD 将延迟原语加载到由 ODELAY_VALUE 属性设置的值。 如果未指定这些属性,则假定值为零。 LD 信号为高电平有效信号,与输入时钟信号 © 同步。

在 VAR_LOAD 模式下,ODELAY 加载端口 LD 将延迟原语加载到由 CNTVALUEIN 设置的值。 CNTVALUEIN[4:0] 处的值将是新的抽头值。 由于此功能,ODELAY_VALUE 属性被忽略。

在 VAR_LOAD_PIPE 模式下,IDELAY 加载端口 LD 加载流水线寄存器中当前的值。 流水线寄存器中的值将是新的抽头值。

流水线寄存器加载 - LDPIPEEN

高电平时,该输入将当前在 CNTVALUEIN 引脚上的值加载到流水线寄存器中。

流水线寄存器复位 - REGRST

当为高电平时,该输入将流水线寄存器复位为全零。

C 引脚极性切换 - CINVCTRL

CINVCTRL 引脚用于动态切换 C 引脚的极性。 这适用于故障不是问题的应用程序。 切换极性时,不要在两个时钟周期内使用 ODELAY 控制引脚。

计数值输入 - CNTVALUEIN

CNTVALUEIN 引脚与 LD 引脚一起用于动态切换可加载抽头值。

计数值输出 - CNTVALUEOUT

CNTVALUEOUT 引脚用于报告加载的抽头值。

增量/减量信号 - CE、INC

增量/减量由使能信号 (CE) 控制。 此接口仅在 ODELAY 处于 VARIABLE、VAR_LOAD 或 VAR_LOAD_PIPE 模式时可用。

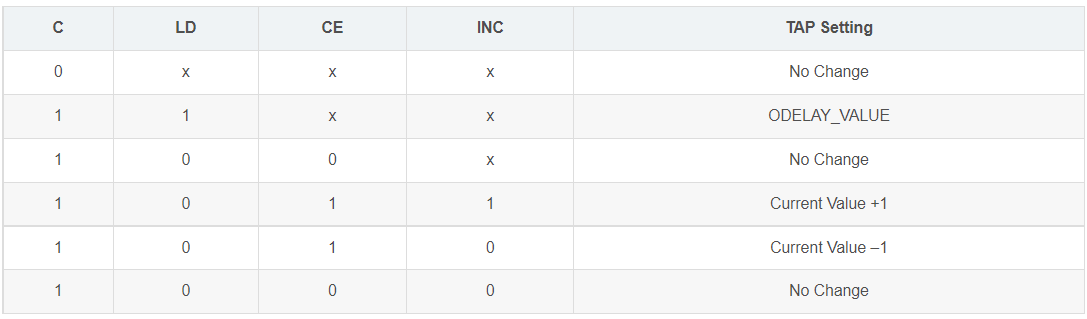

只要 CE 保持高电平,ODELAY 就会在每个时钟 © 周期增加或减少 TIDELAYRESOLUTION。 INC的状态决定ODELAY是递增还是递减; INC = 1 递增,INC = 0 递减,与时钟 © 同步。 如果 CE 为低,则无论 INC 的状态如何,通过 ODELAY 的延迟都不会改变。

当 CE 变为高电平时,递增/递减操作在下一个正时钟周期开始。 当 CE 变为低电平时,递增/递减操作在下一个时钟正沿停止。ODELAYE2 原语中的可编程延迟抽头。 当延迟抽头结束时(抽头 31),后续的递增函数将返回到抽头 0。这同样适用于递减函数:递减到零以下移动到抽头 31。

VAR_LOAD_PIPE 模式下的流水线寄存器功能在总线结构设计中非常有用。 可以使用 LDPIPEEN 一次(管道)加载单个延迟,然后使用 LD p 同时将所有延迟更新到它们的新值。

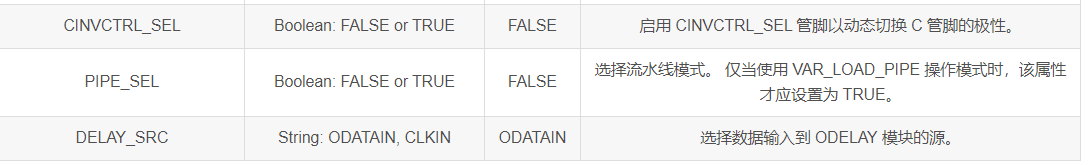

ODELAY 属性

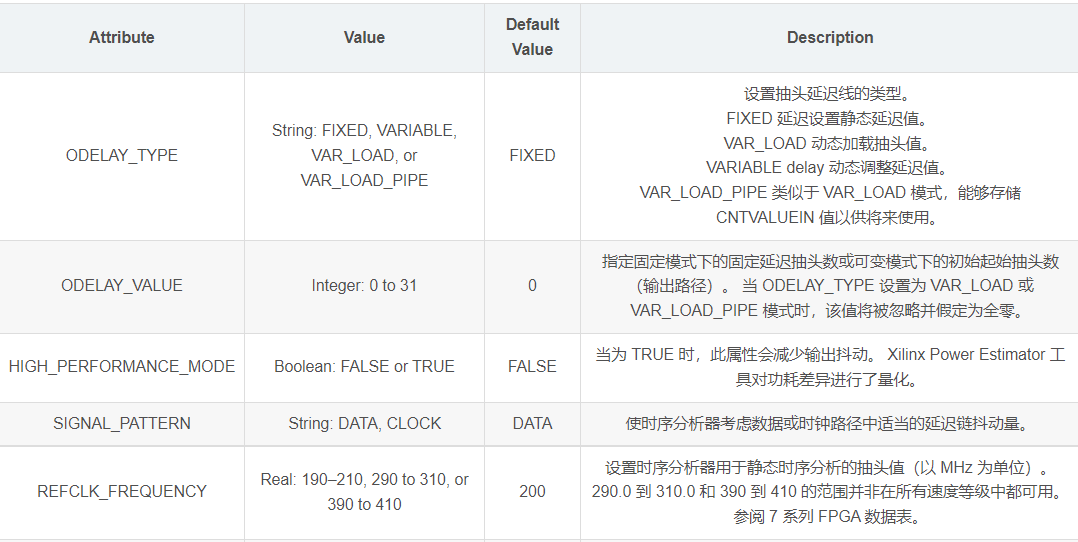

下表总结了 ODELAY 属性

ODELAY_TYPE 属性

当设置为 FIXED 时,抽头延迟值固定为由 ODELAY_VALUE 属性设置确定的抽头数。 该值是预设值,配置后无法更改。

当设置为 VARIABLE 时,选择可变抽头延迟。 可以通过设置 CE = 1 和 INC = 1 来增加抽头延迟,或者通过设置 CE = 1 和 INC = 0 来减少抽头延迟。增加/减少操作与 C 同步。

当设置为 VAR_LOAD 或 VAR_LOAD_PIPE 时,可变抽头延迟可以更改并动态加载。 可以通过设置 CE = 1 和 INC = 1 来增加抽头延迟,或者通过设置 CE = 1 和 INC = 0 来减少抽头延迟。递增/递减操作与 C 同步。VAR_LOAD 模式下的 LD 引脚加载 CNTVALUEIN 上显示的值。 这允许动态设置抽头值。 在 VAR_LOAD_PIPE 模式下,LD 引脚使流水线寄存器中的当前值能够加载到输出延迟中。

ODELAY_VALUE 属性

ODELAY_VALUE 属性指定抽头延迟。 可能的值是 0 到 31 之间的任何整数。默认值为 0。 当通过置位 LD 信号复位抽头延迟时,抽头延迟的值恢复为 ODELAY_VALUE。 在 VAR_LOAD 或 VAR_LOAD_PIPE 模式下,此属性假定为零。

HIGH_PERFORMANCE_MODE 属性

当为 TRUE 时,该属性减少输出抖动。 抖动的这种减少导致 ODELAYE2 原语的功耗略有增加。

SIGNAL_PATTERN 属性

时钟和数据信号具有不同的电气特性,因此在 ODELAY 链中累积不同数量的抖动。 通过设置 SIGNAL_PATTERN 属性,用户启用时序分析器以在计算时序时适当地考虑抖动。 时钟信号本质上是周期性的,没有连续的 1 或 0 的长序列,而数据本质上是随机的,可以有长和短的 1 和 0 序列。

ODELAY 模式

当用作 ODELAY 时,数据输入来自 IBUF 或 FPGA 逻辑,输出到 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2。 有四种可用的操作模式:

- 固定延迟模式 (ODELAY_TYPE = FIXED) :在固定延迟模式中,延迟值在配置时预设为由属性 ODELAY_VALUE 确定的抽头数。 配置后,此值无法更改。 在此模式下使用时,IDELAYCTRL 原语必须被实例化。

- 可变延迟模式(ODELAY_TYPE = VARIABLE) :在可变延迟模式下,延迟值可以在配置后通过操纵控制信号CE 和INC 来改变。在这种模式下使用时,IDELAYCTRL 原语必须被实例化。

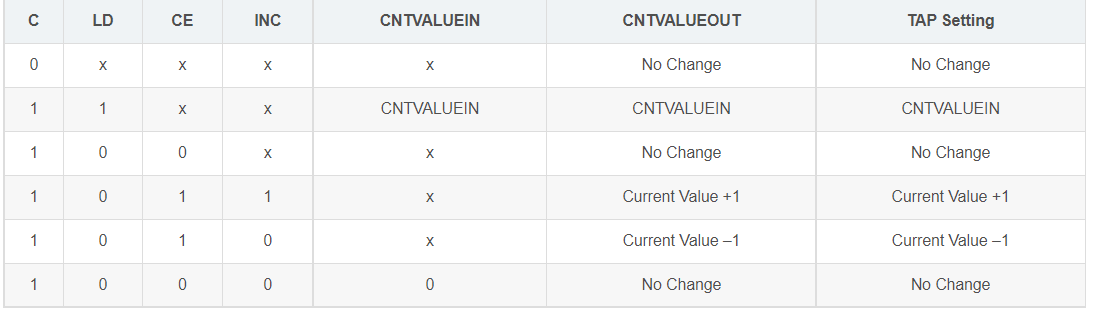

下表中描述了在 VARIABLE 模式下使用的控制引脚。

- 可加载可变延迟模式 (ODELAY_TYPE = VAR_LOAD):除了在此模式下具有与 (ODELAY_TYPE = VARIABLE) 相同的功能外,ODELAY 抽头还可以通过来自 FPGA 逻辑的 5 输入位 CNTVALUEIN< 4:0 > 加载。 当 LD 产生脉冲时,出现在 CNTVALUEIN< 4:0> 处的值将是新的抽头值。 由于此功能,ODELAY_VALUE 属性被忽略。 在此模式下使用时,IDELAYCTRL 原语必须被实例化。

下表描述了在 VAR_LOAD 模式下使用的控制引脚。

ODELAY 时序

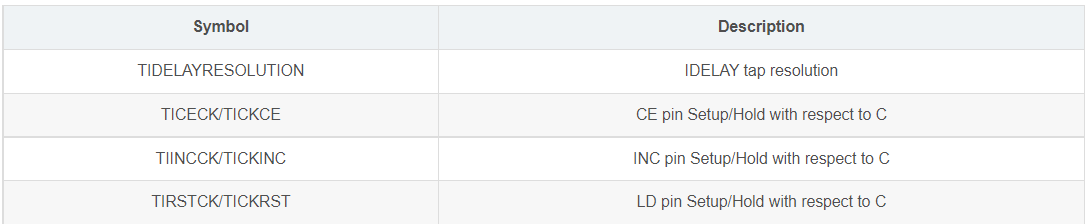

下表显示了 ODELAY 开关特性。

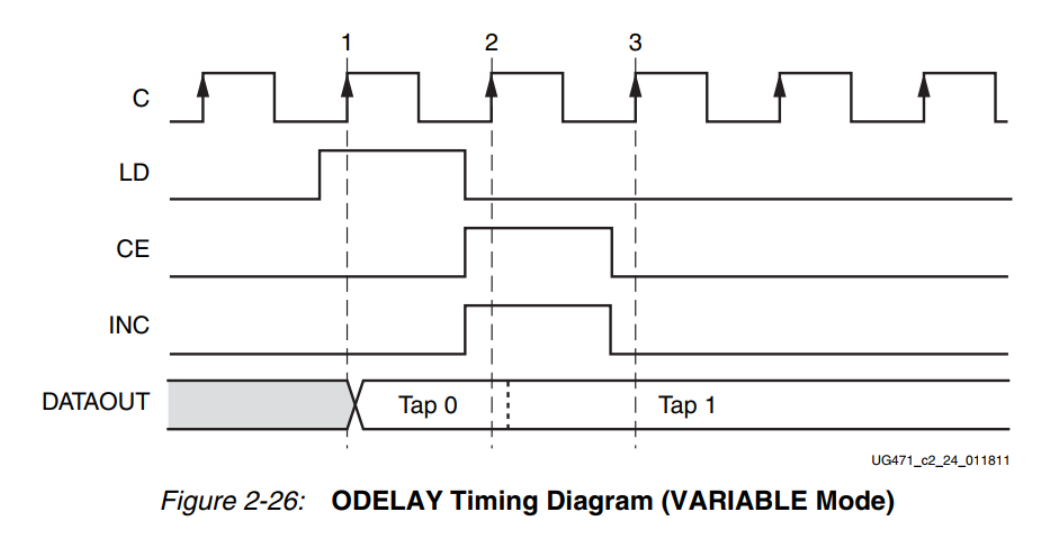

下图显示了 ODELAYE2(ODELAY_TYPE = VARIABLE、ODELAY_VALUE = 0 和 DELAY_SRC = CLKIN/ODATAIN)时序图。

时钟事件 1

在 C 的上升沿,检测到复位(LD 为高电平),导致输出 DATAOUT 选择抽头 0 作为 31 抽头链的输出。

时钟事件 2

在 C 的上升沿捕获 CE 和 INC 上的脉冲。这表示增量操作。 输出从抽头 0 到抽头 1 无毛刺地变化。间后文递增/递减操作后的稳定性。

时钟事件 3

CE 和 INC 不再有效,从而完成递增操作。 输出无限期地保持在抽头 1,直到 LD、CE 或 INC 引脚上有进一步的活动。

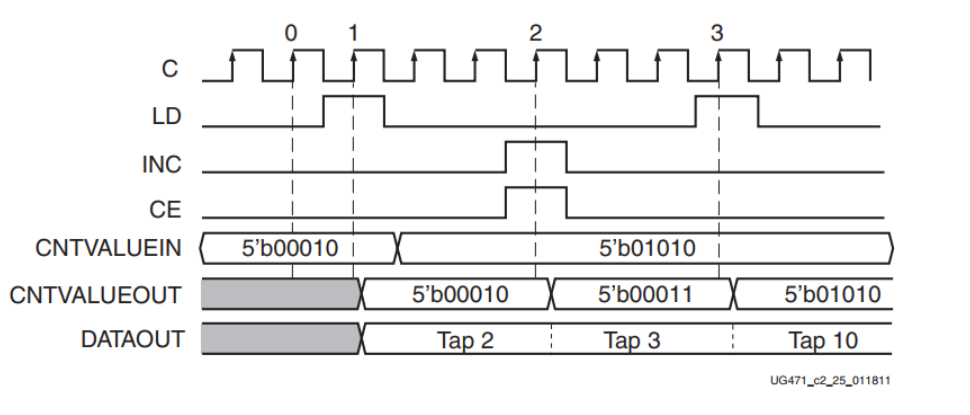

下图显示了在VAR_LOAD模式下的ODELAY 时序图。

时钟事件 0

在 LD 产生脉冲之前,抽头设置和 CNTVALUEOUT 处于未知值。

时钟事件 1

在 C 的上升沿,LD 被检测为高电平,导致输出 DATAOUT 等于 CNTINVALUE,并将抽头设置更改为抽头 2。更新 CNTVALUEOUT 以表示新的抽头值。

时钟事件 2

在 C 的上升沿捕获 CE 和 INC 上的脉冲。这表示增量操作。 输出从抽头 2 到抽头 3 无毛刺地变化。CNTVALUEOUT 被更新以表示新的抽头值。

时钟事件 3

在 C 的上升沿,检测到一个 LD,导致输出 DATAOUT 等于 CNTINVALUE。 CNTVALUEOUT 显示抽头设置的值。 输出将无限期地保持在抽头 10,直到 LD、CE 或 INC 引脚上有进一步的活动。

递增/递减操作后的稳定性

图 2-26 显示了响应 INC 和 CE 命令的 ODELAY 线从抽头 0 变为抽头 1。 显然,当抽头 0 处的数据值与抽头 1 处的数据值不同时,输出必须改变状态。 但是,当抽头 0 和抽头 1 处的数据值相同(例如,两者均为 0 或均为 1)时,从抽头 0 到抽头 1 的转换不会导致输出出现故障或中断。 通过想象发送器数据信号通过 ODELAY 抽头链,可以更好地理解这个概念。 如果抽头 0 和抽头 1 都在发射信号的中心附近,则抽头 0 处的数据与抽头 1 处的数据没有区别。在这种情况下,从抽头 0 到抽头 1 的转换不会导致输出发生变化 . 为确保这种情况,ODELAY 的递增/递减操作被设计为无故障。

因此,用户可以在实时用户数据通过 ODELAYE2 原语时实时动态调整 ODELAY 抽头设置。 只要当前延迟线值接近传输数据信号的中心,这些调整就不会中断实时用户数据。

当在时钟信号路径中使用 ODELAYE2 原语时,无毛刺行为也适用。 调整抽头设置不会导致输出出现故障或中断。

reference

- UG471