module edge_detect(

clk,

rstn,

signal_a,

pos_edge_flag,

neg_edge_flag

);

input clk,rst;

input signal_a;

output pos_edge_flag, neg_edge_flag;

reg signal_reg_1,signal_reg_2;

//sync

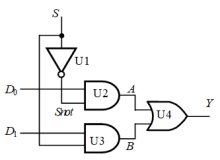

always @(posedge clk or negedge rstn) begin

if (!rstn)

{signal_reg_2,signal_reg_1} <= 2'b00;

else

{signal_reg_2,signal_reg_1} <= {signal_reg_1,signal_a};

end

//pos_edge falg pull up

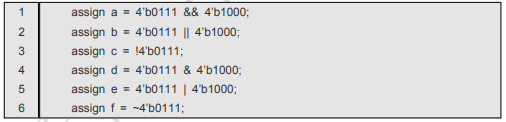

assign pos_edge_flag = signal_reg_1 & !signal_reg_2;

//neg_edge falg pull up

assign neg_edge_flag = !signal_reg_1 & signal_reg_2;

endmodule