一. 设计要求

八位数字抢答器设计要求:

抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

设置一个系统清除和抢答控制开关S,该开关由主持人控制。

抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如,30秒)。当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00

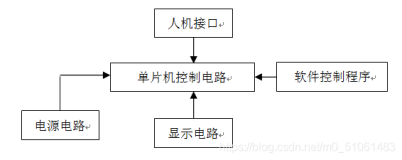

二. 程序分析

程序使用到的硬件有: 按键,数码管,蜂鸣器,三个硬件的驱动模块可以提前写好(gzh中都已给出相应的教程),编写完成后,就是按照要求编写逻辑代码,最简单的方法是使用状态机进行控制。

按键一共需要使用到10个 :8个用于抢答,2个用于控制

数码管一共需要使用到3个: 2个用于显示倒计时,1个用于显示选手编号

三. 数码管驱动程序修改

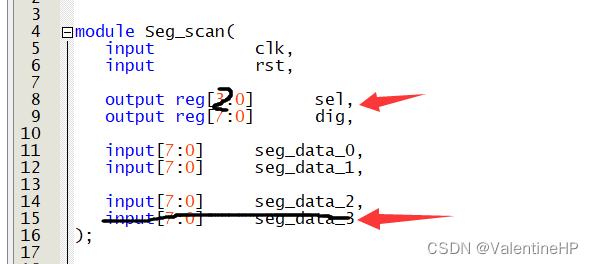

之前编写的驱动程序是四个数码管显示,需要将其修改为三个数码管显示,修改如下,将sel位宽修改为3,并将数码管4上显示的数据删除,

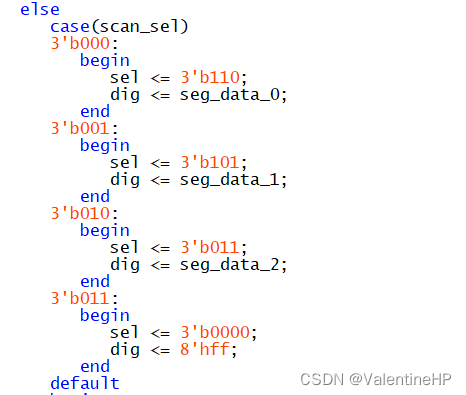

然后将动态扫描代码修改为如下

就将数码管驱动需要修改的部分修改完成啦

其他模块均不需要修改。

四. 代码编写

首先,需要确定各个状态是怎么样的,每个状态之间是如何跳转的。本次设计的状态如下

空闲态 : 此时抢答器处于空闲的状态,当主持人按下开始按键后,进入到激活态

激活态: 此时选手可以进行抢答,抢答成功后,进入有效态,否则倒计时为0时,进入到无效态

有效态: 倒计时停止,数码管上显示抢答选手的编号。主持人按下清除按键进入到空闲态

无效态: 倒计时保持为0,主持人按下清除按键进入到空闲态

对应代码如下

always@(*) begin case(state) S_IDLE: if( begin_key == 1'b1) //开始抢答 next_state <= S_ACTIVE; else next_state <= S_IDLE; S_ACTIVE: if( sec_ack == 1'b1 ) //时间结束无效抢答 next_state <= S_UnValue; else if( player_keys != 8'hff) //有效抢答 next_state <= S_Value; else next_state <= S_ACTIVE; S_UnValue: if( clear_key == 1'b1 ) //抢答结束清除 next_state <= S_IDLE; else next_state <= S_UnValue; S_Value: if( clear_key == 1'b1 ) //抢答结束清除 next_state <= S_IDLE; else next_state <= S_Value; default: next_state <= S_IDLE; endcase end

选手编号统计,当按键按下的时候,寄存当前选手的编号,并且状态转移,再次按下时,无效

always@(posedge sys_clk) begin if( player_keys == 8'b1111_1110 && state == S_ACTIVE) player_numb <= 'd1; else if(player_keys == 8'b1111_1101 && state == S_ACTIVE ) player_numb <= 'd2; else if(player_keys == 8'b1111_1011 && state == S_ACTIVE ) player_numb <= 'd3; else if(player_keys == 8'b1111_0111 && state == S_ACTIVE ) player_numb <= 'd4; else if(player_keys == 8'b1110_111 && state == S_ACTIVE ) player_numb <= 'd5; else if(player_keys == 8'b1101_111 && state == S_ACTIVE ) player_numb <= 'd6; else if(player_keys == 8'b1011_111 && state == S_ACTIVE ) player_numb <= 'd7; else if(player_keys == 8'b0111_111 && state == S_ACTIVE ) player_numb <= 'd8; else if( clear_key == 1'b1 ) player_numb <= 'd0; else player_numb <= player_numb; end

这样核心代码就编写完成了。

需要完整代码的可以关注微信公众号 FPGA之旅 回复 八位数字抢答器 获取完整代码

公众号:FPGA之旅