不多啰嗦,接着上文继续读文档吧:

初始化

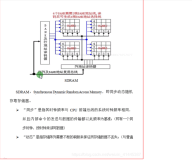

SDRAM上电后必须初始化,初始化的过程:

- 上电、时钟稳定、DQM高、CKE高

- 100微秒等待,期间除了INHIBIT或NOP命令,其他命令都不能有。至少1个INHIBIT或NOP

- PRECHARGE命令

- 两个自动刷新命令

- 配置模式寄存器

对照时序图操作:

上面出现了一些定义的时间,我们也可以在文档中看到具体内容:

配置模式寄存器

The mode register is used to define the specific mode of operation of the SDRAM. This definition includes the selection of a burst length, a burst type, a CAS latency, an operating mode and a write burst mode, as shown in MODE REGISTER DEFINITION.The mode register is programmed via the LOAD MODE REGISTER command and will retain the stored information until it is programmed again or the device loses power. Mode register bits M0-M2 specify the burst length, M3 specifies the type of burst (sequential or interleaved) , M4- M6 specify the CAS latency, M7 and M8 specify the operating mode, M9 specifies the WRITE burst mode, and M10 and M11 are reserved for future use.

The mode register must be loaded when all banks are idle, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

模式寄存器用于定义SDRAM的特定操作模式。该定义包括突发长度、突发类型、CAS延迟、操作模式和写突发模式的选择,如模式寄存器定义所示。模式寄存器通过负载模式寄存器命令进行编程,并将保留存储的信息,直到再次编程或设备断电。模式寄存器位M0-M2指定突发长度,M3指定突发类型(顺序或交织),M4- M6指定CAS延迟,M7和M8指定操作模式,M9指定写突发模式,M10和M11保留供将来使用。

当所有BANK空闲时,必须加载模式寄存器,控制器必须等待指定的时间才能启动后续操作。违反这些要求中的任何一个都会导致未指定的操作。