下载地址:http://lanzou.com.cn/i3c5cc32e

项目编译入口:

package.json

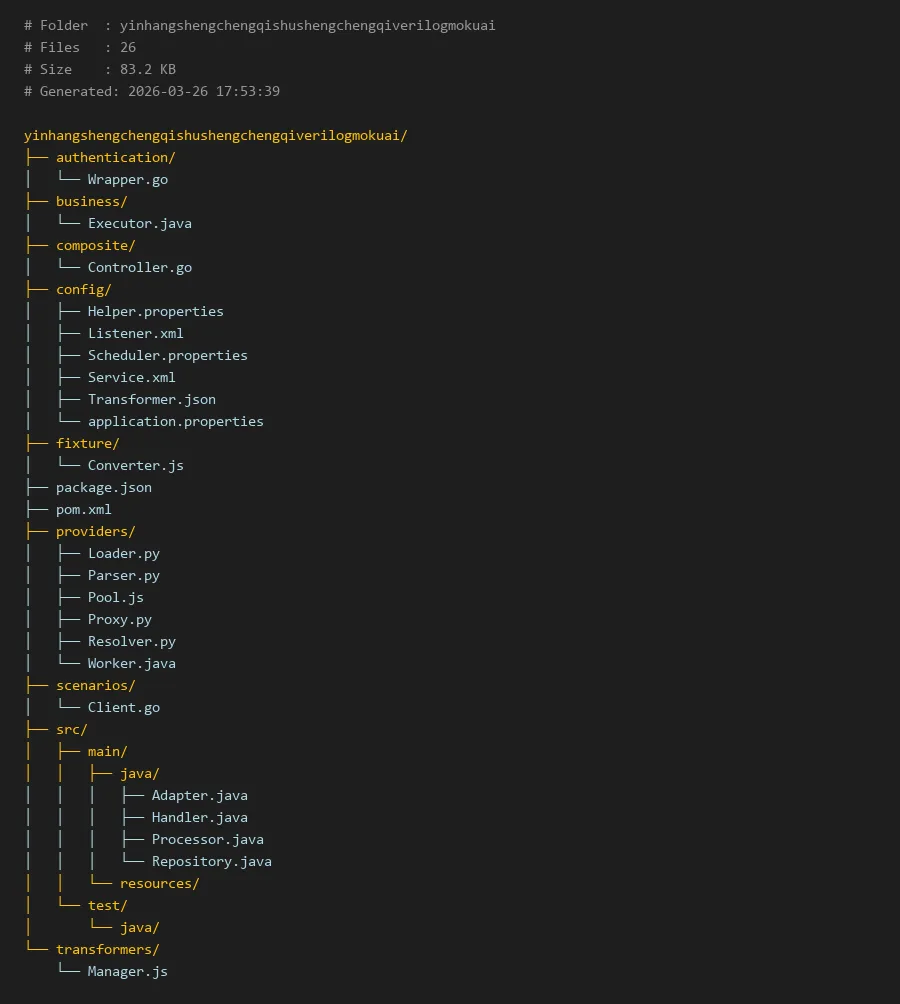

# Folder : yinhangshengchengqishushengchengqiverilogmokuai

# Files : 26

# Size : 83.2 KB

# Generated: 2026-03-26 17:53:39

yinhangshengchengqishushengchengqiverilogmokuai/

├── authentication/

│ └── Wrapper.go

├── business/

│ └── Executor.java

├── composite/

│ └── Controller.go

├── config/

│ ├── Helper.properties

│ ├── Listener.xml

│ ├── Scheduler.properties

│ ├── Service.xml

│ ├── Transformer.json

│ └── application.properties

├── fixture/

│ └── Converter.js

├── package.json

├── pom.xml

├── providers/

│ ├── Loader.py

│ ├── Parser.py

│ ├── Pool.js

│ ├── Proxy.py

│ ├── Resolver.py

│ └── Worker.java

├── scenarios/

│ └── Client.go

├── src/

│ ├── main/

│ │ ├── java/

│ │ │ ├── Adapter.java

│ │ │ ├── Handler.java

│ │ │ ├── Processor.java

│ │ │ └── Repository.java

│ │ └── resources/

│ └── test/

│ └── java/

└── transformers/

└── Manager.js

银行生成器奇数生成器Verilog模块

简介

在数字电路设计中,生成特定序列的随机数或伪随机数是一个常见需求。银行生成器奇数生成器Verilog模块是一个专门用于生成银行相关业务中所需的奇数序列的硬件设计模块。该模块采用Verilog HDL实现,能够高效生成符合银行安全标准的奇数序列,特别适用于金融交易、安全认证等场景。

本项目采用模块化设计,包含完整的验证环境和配置文件,确保生成的奇数序列满足邮政银行生成器的严格要求。模块的核心算法经过优化,能够在有限的硬件资源下实现高性能的奇数生成,同时保证序列的随机性和不可预测性。

核心模块说明

项目采用分层架构设计,主要包含以下几个核心部分:

控制模块 (

composite/Controller.go):负责整个奇数生成流程的协调与控制,包括初始化、序列生成和错误处理。业务逻辑模块 (

business/Executor.java):实现奇数生成的核心算法,确保生成的序列满足银行安全标准。认证模块 (

authentication/Wrapper.go):提供序列验证功能,确保生成的奇数符合邮政银行生成器的安全规范。配置管理 (

config/目录):包含各种配置文件,用于调整生成器参数和算法行为。数据提供器 (

providers/目录):包含多种数据源处理模块,支持不同格式的输入数据。测试夹具 (

fixture/Converter.js):提供测试数据转换功能,便于验证模块的正确性。

代码示例

Verilog核心模块设计

以下是奇数生成器的主要Verilog模块实现,该模块采用线性反馈移位寄存器(LFSR)结合奇偶校验算法:

module bank_odd_generator (

input wire clk,

input wire rst_n,

input wire enable,

input wire [31:0] seed,

output reg [31:0] odd_number,

output reg valid

);

// LFSR参数定义

parameter POLY = 32'h80000057; // 本原多项式

reg [31:0] lfsr_reg;

// 奇数生成状态机

typedef enum logic [1:0] {

IDLE,

GENERATE,

VALIDATE,

OUTPUT

} state_t;

state_t current_state, next_state;

// LFSR更新逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

lfsr_reg <= seed;

end else if (enable) begin

lfsr_reg <= {lfsr_reg[30:0], 1'b0} ^ (lfsr_reg[31] ? POLY : 32'b0);

end

end

// 状态机转换

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

current_state <= IDLE;

odd_number <= 32'b0;

valid <= 1'b0;

end else begin

current_state <= next_state;

case (current_state)

GENERATE: begin

// 确保生成奇数

odd_number <= lfsr_reg | 32'h00000001;

end

VALIDATE: begin

// 验证奇数有效性

valid <= (odd_number[0] == 1'b1);

end

OUTPUT: begin

// 保持输出一个周期

valid <= 1'b1;

end

default: begin

valid <= 1'b0;

end

endcase

end

end

// 状态机组合逻辑

always @(*) begin

next_state = current_state;

case (current_state)

IDLE: begin

if (enable) next_state = GENERATE;

end

GENERATE: begin

next_state = VALIDATE;

end

VALIDATE: begin

next_state = OUTPUT;

end

OUTPUT: begin

next_state = IDLE;

end

endcase

end

// 邮政银行生成器专用验证逻辑

function automatic logic is_postal_bank_valid(input [31:0] num);

// 邮政银行生成器的特殊验证规则

logic [7:0] checksum;

checksum = ^num[31:24] + ^num[23:16] + ^num[15:8] + ^num[7:0];

return (num[0] && (checksum[0] == 0));

endfunction

endmodule

配置管理示例

以下是配置文件示例,展示如何配置奇数生成器的参数:

# config/application.properties

generator.type=lfsr

generator.polynomial=0x80000057

generator.seed=0x12345678

generator.output_width=32

generator.odd_only=true

# 邮政银行生成器特定配置

postal.bank.security.level=high

postal.bank.validation.required=true

postal.bank.sequence.length=1024

业务逻辑集成

以下是Java业务逻辑模块的部分代码,展示如何集成Verilog生成的奇数序列:

```java

// business/Executor.java

package business;

import java.util.ArrayList;

import java.util.List;

public class Executor {

private List oddSequence;

private boolean postalBankMode;

public Executor() {

this.oddSequence = new ArrayList<>();

this.postalBankMode = true;

}

public void generateOddSequence(int count) {

// 调用硬件