一、独立仿真

文件夹建立

以工程4位二进制计数器为例,首先在工作目录下建立工程文件夹,其中count4用于存放编写的Verilog HDL代码,而count4_tb则用于存放要输入给Verilog HDL代码的波形信号,也就是testbench文件。

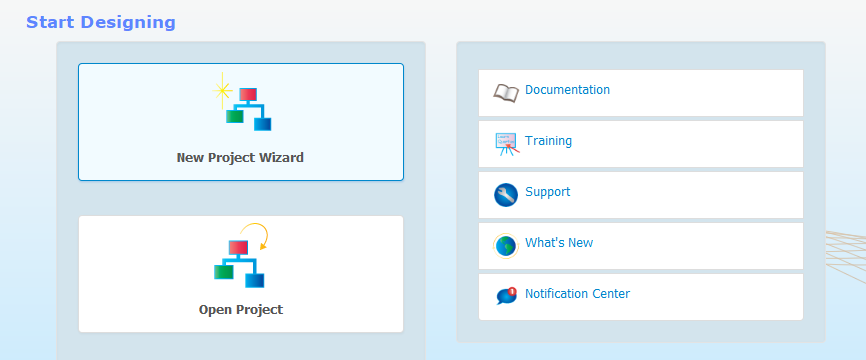

建立quartus II工程文件

运行quartus II后点击New Project Wizard建立一个新的工程。

选择工作区域时选择在文件夹建立章节中建立的count4文件夹,并命名工程名为count4,顶层设计名称默认为工程名,可根据自己需求进行改动。

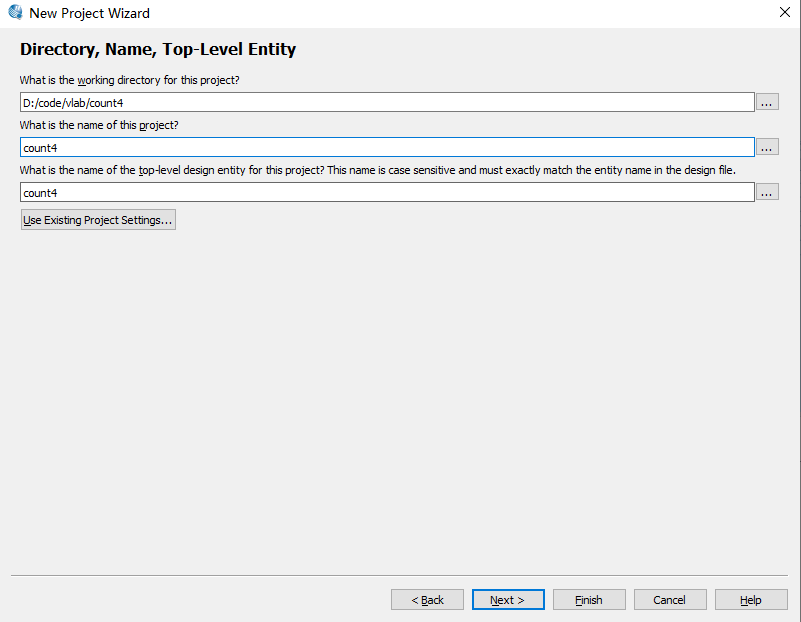

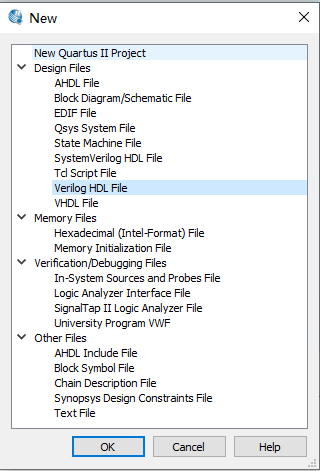

VerilogHDL代码编写并编译

工程建立后在工程中建立或者添加Verilog HDL文件,并将代码写入其中保存。可以通过窗口顶部菜单栏中File->New或者工具栏中的新建文件快捷按钮进行文件创建。

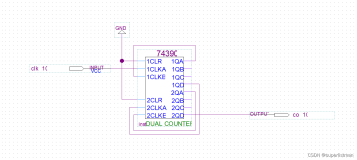

通过VerilogHDL语言编写4位二进制计数器,示例代码如下:

module count4(clk,r,s,en,d,q,co);

input clk,r,s,en;

input [3:0] d;

output [3:0] q;

output co;

reg [3:0] q;

reg co;

always@(posedge clk)

if(r) q=0;

else

begin

if(s) q=d;

else if(en)

begin

q = q+1;

if(q==4'b1111) co=1;

else co=0;

end

else q=q;

end

endmodule

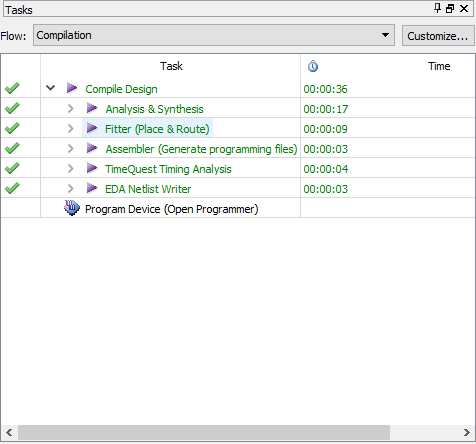

编写完成后对代码进行编译,可以通过窗口顶部菜单栏中Processing->Start Compilation或工具栏中Start Compilation按钮进行编译。编译通过后任务栏将如下图所示。

在ModelSim中进行仿真

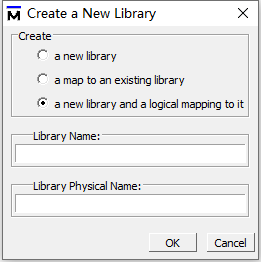

打开ModelSim后首先新建工作库,通过窗口顶部菜单栏中File->New->library或在library窗口中右键New->library中新建工作库

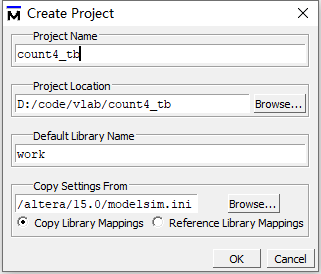

工作库建立完成后通过File->New->Project建立工程,其中工程目录选定在文件夹建立章节中建立的count4_tb文件夹,工程名为count4_tb。

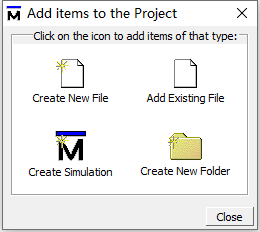

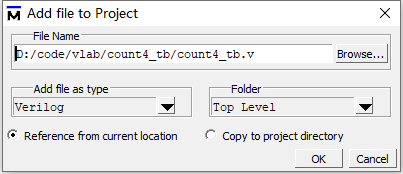

在工程中通过Add Existing File加入编写好的元件并通过Create New File新建用于输入测试信号的Testbench文件count4_tb.v,其中testbench文件类型应选择Verilog。

count4_tb.v文件中应写入testbench,具体代码如下:

`timescale 1ns/1ns // 仿真时间精度

module count4_tb;

reg clk,r,s,en; // 器件的输入信号在testbench中类型为reg

reg [3:0] d;

wire [3:0] q; // 器件的输入信号在testbench中类型为wire

wire co;

initial // initial中的信号将会顺序执行一次

begin

clk=0;r=1;s=0;en=1;d=4'b1001; // 0ns时信号的初始值

#300 r=0; // 300ns时r为0

#200 s=1; // 500ns时s为1

#200 s=0; // 700ns时s为0

#1000 en=0; // 1700ns时en为0

#300 $stop; // 2000ns时仿真结束

end

always #50 clk=~clk; // always中的信号将会循环执行,此处为每50ns对clk信号执行一次取反输入

count4 mycount4(.clk(clk),.r(r),.s(s),.en(en),.d(d),.q(q),.co(co));

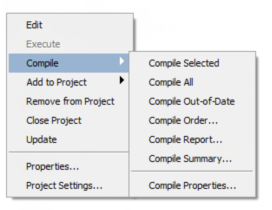

endmodule对count4和count4_tb进行编译,选择Compilation All即可。编译通过后文件status将会变为绿色对号标记。

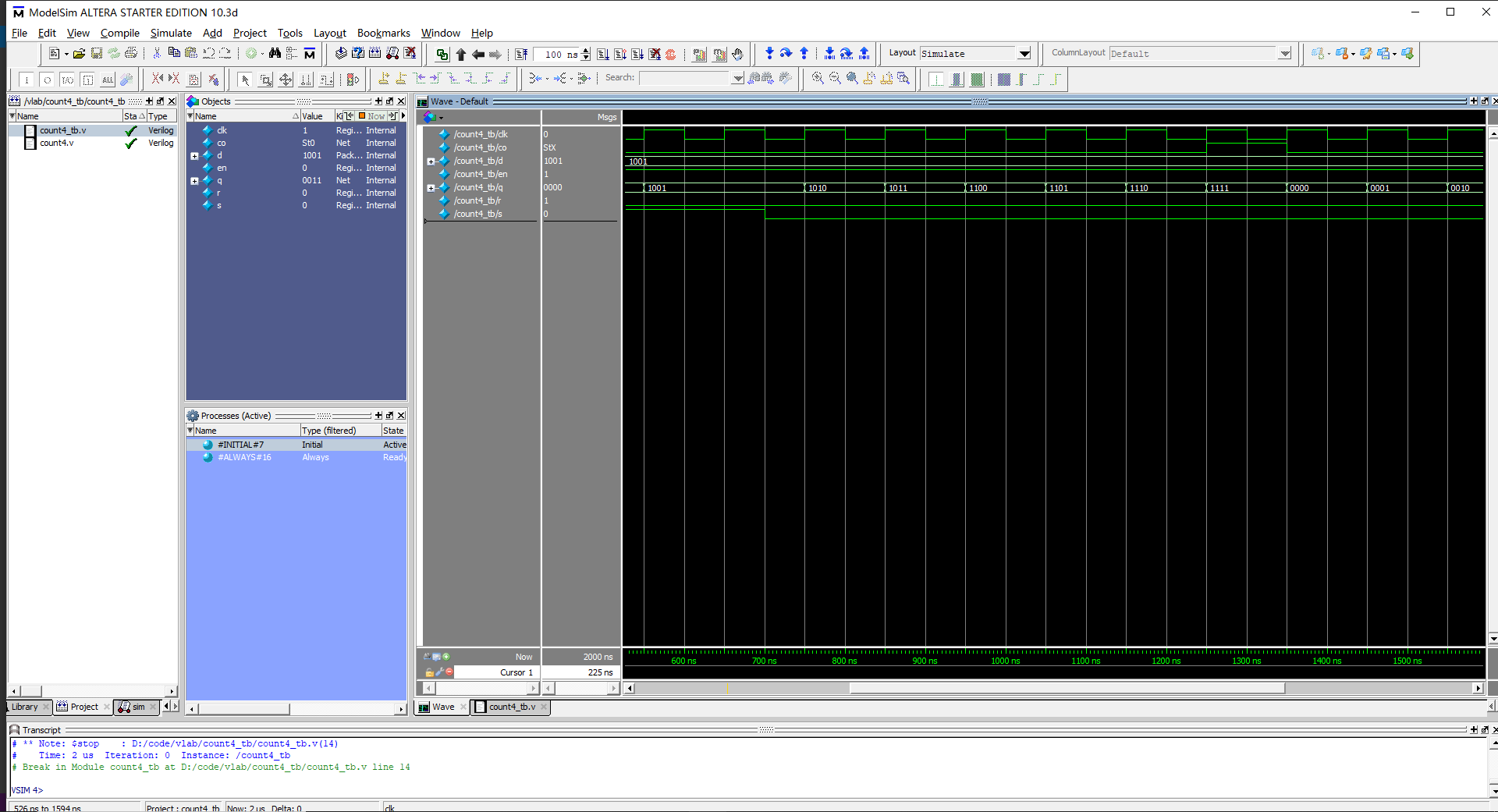

波形仿真

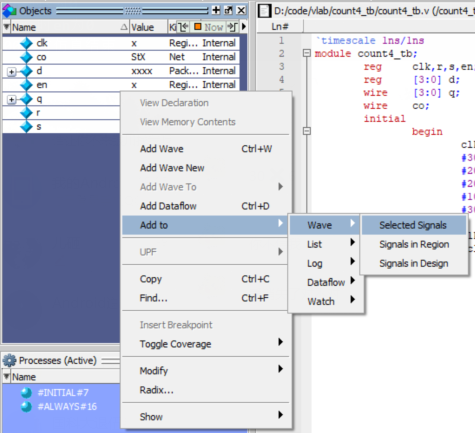

编译通过后通过顶部菜单栏Simulate->Start Simulation选择count4_tb文件进行仿真。将Objects中的信号全部选中添加到wave中,并点击顶部菜单栏Simulate->run->run-all得到波形仿真结果

二、联合仿真

quartus II 提供了对仿真工具的调用接口,可以通过调用这些接口来实现更方便的联合仿真。联合仿真步骤如下。

创建testbench模板

在VerilogHDL代码编写并编译之后,可以通过顶部菜单栏中Processing->Start->Start Test Bench Template Wirter来创建Testbench模板。新创建的Testbench模板文件存储为当前文件夹下./simulation/modelsim/count4.vht文件,可以通过quartus II或其他文本编辑工具打开并修改为自己所需的testbench,Testbench各部分内容作用在ModelSim中进行仿真已经给出。

联合仿真设置

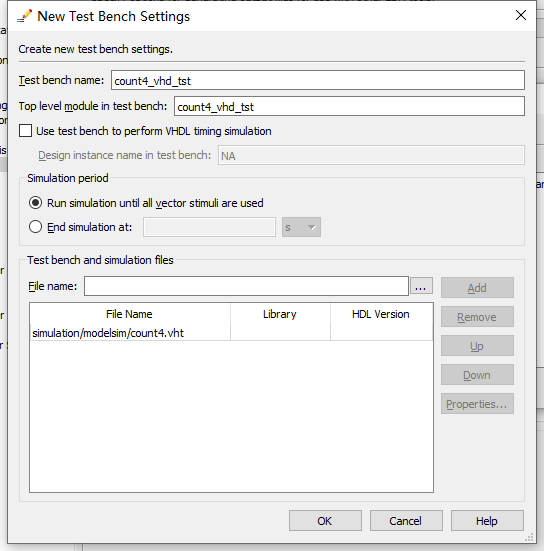

在窗口顶部菜单栏Assignments->Settings->EDA Tool Settings中选择Simulation为ModelSim或者ModelSim-Altera。具体取决于你装的什么EDA工具。Assignments->Settings->Simulation中选择使用的Testbench文件。其中test bench name选项中应该填写testbench中module名。

开始联合仿真

选择窗口顶部菜单栏Tools->Run Simulation Tools->RTL simulation(此功能为RTL功能仿真,Gate Level Simulation为门级仿真,根据自己需求自选)。

此后步骤与波形仿真中步骤相同。