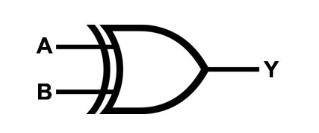

在数字电子和逻辑电路的广阔世界中,异或门是一个基本构建块,在信息处理中发挥着至关重要的作用。XOR ,异或的缩写,它是一种逻辑运算,当高电平输入的数量为奇数时,产生高电平输出;当低电平输入的数量为偶数时,产生低电平输出。这种独特的特性使异或门成为各种应用中的重要组成部分,从简单的二进制算术到复杂的数据加密算法。

在本文中,我们将探讨异或门的内部工作原理,包括其真值表、逻辑符号表示、电路图以及使用晶体管的实际构造。

什么是异或逻辑门?

异或门也称为异或门。电子异或门执行数字逻辑异或功能。此函数通常类似于标准 OR 函数,但有一个关键区别。对于 OR 和 XOR,当两个输入中的任何一个输入为高电平时,输出为高电平,当两个输入都为低电平时,输出为低电平。

然而,当两个输入均设置为高状态时,标准OR电路将产生高输出信号,而XOR电路将产生低输出信号。这种基本行为被称为异或门。在最简单的异或门设计中,只需要 5 个晶体管。

异或门真值表

输入 |

输出 |

|

A |

B |

是 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

该门的布尔表达式为

Y = (A ⊕ B)

输出

(A ⊕ B) = AB + AB

上面的真值表清楚地表明,只有当异或门的两个输入端子处于彼此不同的逻辑电平时,异或门的输出才会变为“高”。如果这两个输入 A 和 B 均处于逻辑电平“ 1 ”或均处于逻辑电平“ 0 ”,则输出为“ 0 ”。

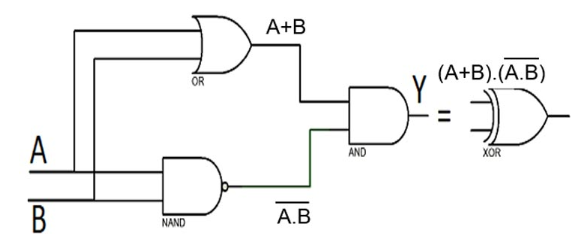

异或门逻辑图

从上面的逻辑图中可以看出,异或门是通过组合三种不同类型的逻辑门( 或门、与非门和 与门)来构建的 ,以产生所需的结果。

构建异或门所需的组件

因此,只需很少的元件,我们就可以构建一个异或门电路。

- 2N2222 (NPN) 晶体管 x5

- 10kΩ电阻x3

- 220Ω电阻x3

- 按钮 x2

- 面包板 x1

- 9V电池×1

- LED 和连接线

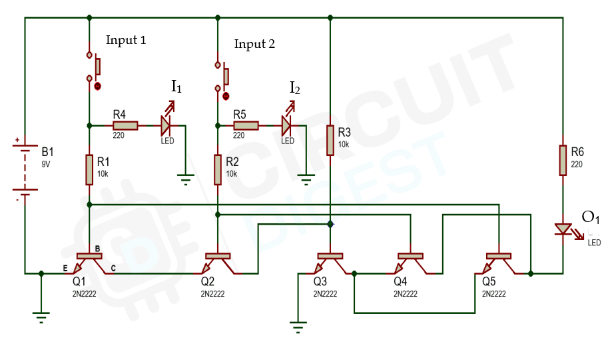

使用晶体管的异或门电路图

下面的电路图说明了使用5 个 NPN 晶体管的异或门。这里,I 1和I 2代表两个输入,O 1代表输出。

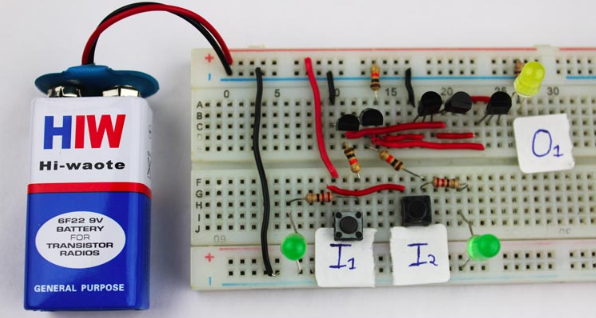

图为使用5个晶体管的简单异或门电路。在布局中,输入 A 和 B 均连接至 9V 电源。不同颜色的连接线有助于查看连接。如果电线的放置有任何歧义,可以参考电路图。

门设计是左侧两个晶体管的与非门,中间晶体管的开关,最后两个晶体管的或门。

检查照片中显示的配置后,很明显,最右侧电阻器产生的电流至少无法到达地面,导致 LED 保持关闭状态。其背后的原因在于,左侧第一个电阻产生的所有电流都流向第一地。因此,由于进入第三晶体管基极的电压不足,开关保持在断开位置。

如果一个输入被激活,电流就有能力从最右边的晶体管流到第二个地。最后,当两个输入均被停用时,输出保持关闭状态,因为电流无法进入或门晶体管的基极。这种配置可防止电流从最右侧的电阻器流向第二个接地端。

应用领域

从密码学的深度到错误检测领域,异或门被证明是不可或缺的盟友。它具有执行按位运算的能力,可以进行二进制加法和减法,确保数据完整性,甚至生成奇偶校验。该门的多功能性和优雅性巩固了其在无数数字系统中的作用,为塑造现代世界的技术进步铺平了道路。

注:本文有IC先生网www.mrchip.cn编辑整理发布,请勿转载,谢谢!