1)高性能应用处理:C910

玄铁C910采用12级多发乱序流水线,典型工作频率>2.5GHz,是首款实现规模化量产的高性能乱序RISC-V处理器。采用3发射、8执行的深度乱序执行架构,针对算术运算、内存访问以及多核同步等方面进行了增强。可以应用在对通用性能要求较高的高性能消费终端、边缘计算等场景。

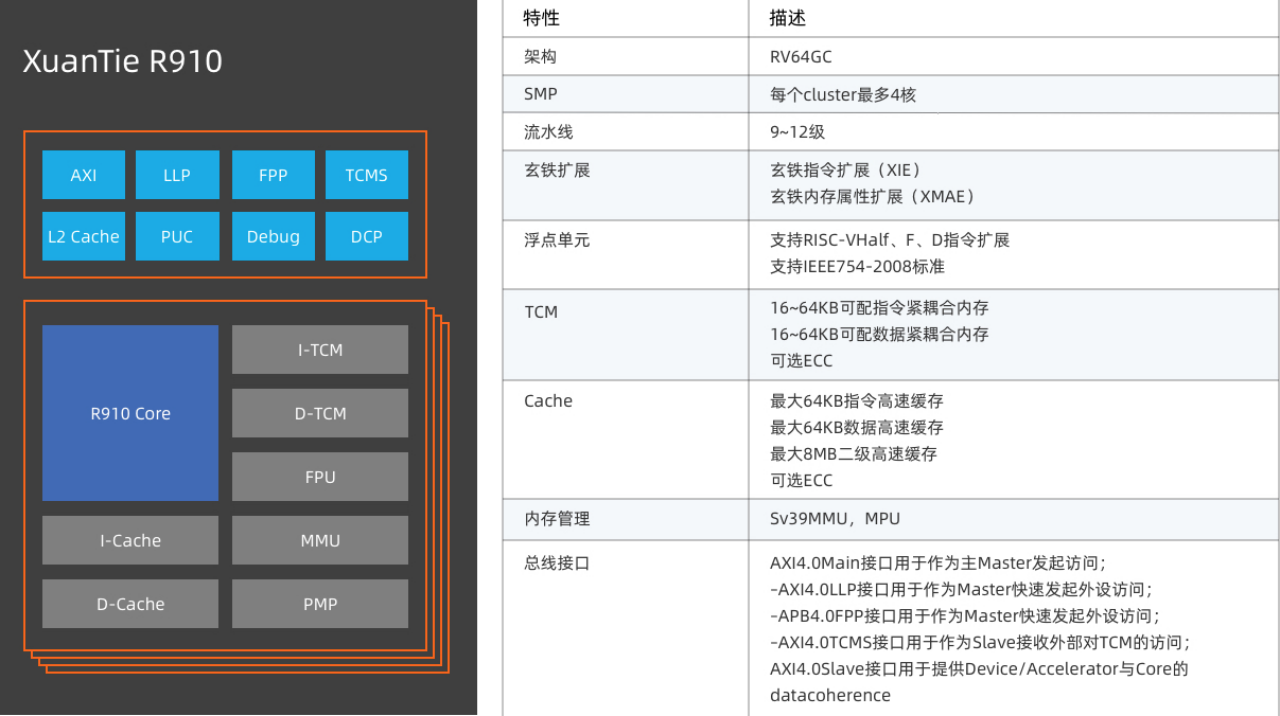

2)可靠实时增强:R910

a)概述

玄铁R910用12级多发乱序流水线,典型工作频率>2.5GHz,同时支持Cache以及TCM存储架构,各级片上存储支持校验纠错以提升可靠性,可进一步选配快速外设接口以及一致性外设接口,从而大幅提升系统实时性。可以应用在对实时性及算力有高要求的企业级SSD,网络通信等场景。

R910核心主要特点:

b)处理器简介

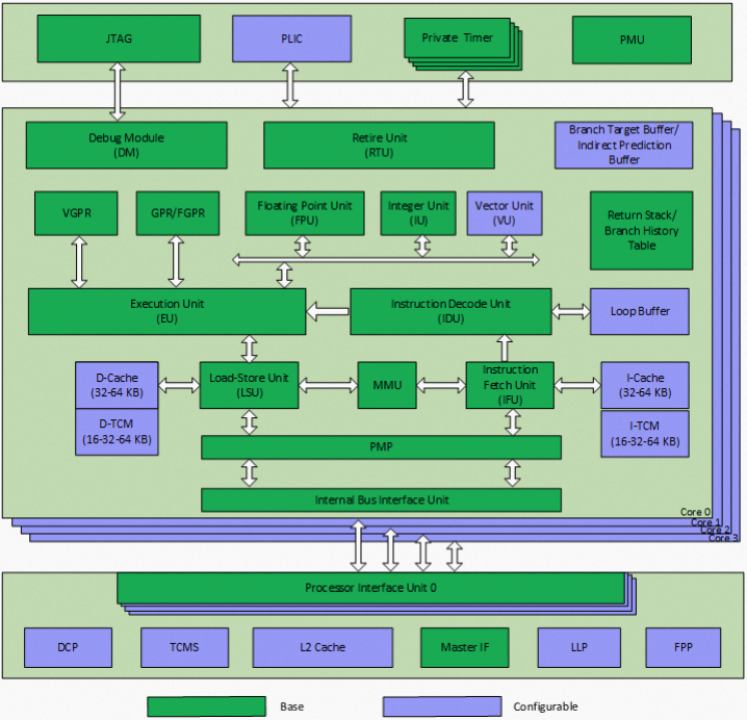

R910MP结构框图如下所示。

R910核内子系统主要包含:指令提取单元(IFU)、指令译码单元(IDU)、整型执行单元(IU)、浮点单元(FPU)、存储载入单元(LSU)、指令退休单元(RTU)、虚拟内存管理单元(MMU)和物理内存保护单元(PMP)。

R910多核子系统包含:数据一致性接口单元(CIU)、二级高速缓存、主设备接口单元、可配置的快速外设访问接口(LLP)、可配置的APB主设备接口(FPP)、可配置的紧耦合内存访问接口(TCMSP)、可配置的AXI4.0设备一致性接口(DCP,Device Coherence Port)、平台级中断控制器(PLIC)、计时器和自定义多核单端口调试框架。