1)入门级微控制器:E902

a)概述

玄铁E902采用2级极简流水线并对执行效率进行了增强,典型工作频率>150MHz,是首款支持硬件安全扩展技术的RISC-V处理器。可以应用在对功耗和成本极其敏感的IoT、MCU等场景。

E902处理器体系结构的主要特点如下:

b)处理器简介

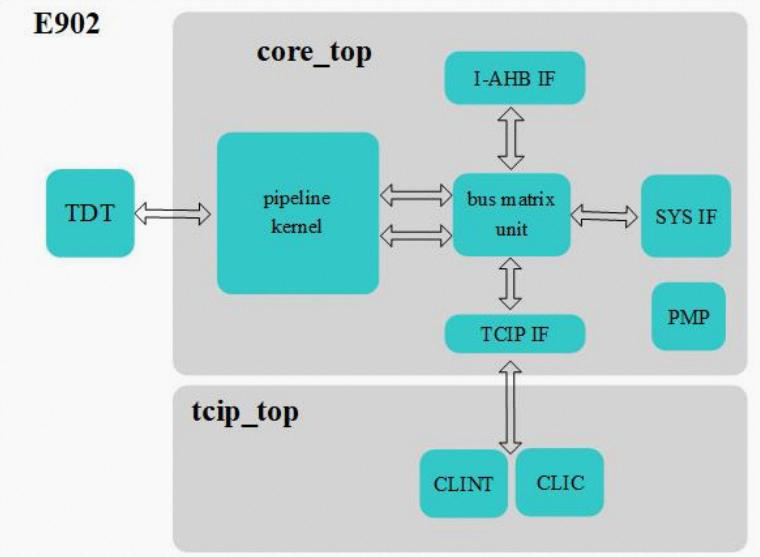

E902的结构框图如下所示:

结构图E902处理器采用2级流水线结构:取指和执行。指令取指阶段主要负责从内存中获取指令;指令执行阶段主要负责指令译码、执行和回写。

可配置的物理内存保护单元(Physical Memory Protection,PMP)负责物理地址的权限检查实现内存的保护功能,权限可划分为:不可读写/只读/可读写,可执行/不可执行。

TDT调试单元(T-Head Debug Trace)支持各种调试方式,包括软件断点、内存断点、单步和多步的指令跟踪等多种方式,可在线调试CPU、通用寄存器(GPR)、控制寄存器(CSR)和内存。

E902设计有片上紧耦合的IP接口和多条AHB-Lite的总线接口。片上紧耦合的IP接口集成处理器中断控制器(CLIC),支持中断嵌套以及处理器核局部中断(CLINT)。外部中断源数量最高可配置240个,中断优先级支持4/8/16/32级可配置。

2)高能效微控制器:E906

a)概述

玄铁E906采用5级按序流水线,典型工作频率>1GHz,可选性能优异的单精度浮点单元以及标量DSP计算单元。可以应用在无线接入、音频、中高端MCU、导航等场景。

E906处理器体系结构的主要特点如下:

b)处理器简介

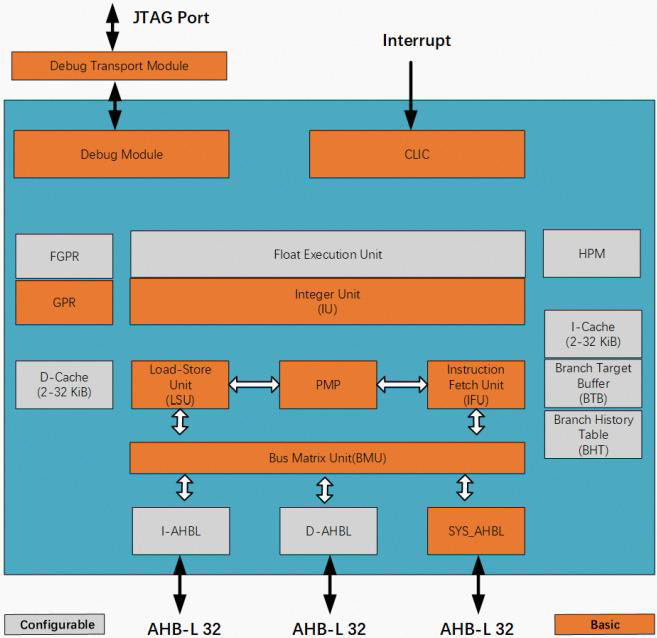

E906的结构框图如下所示:

E906处理器采用5级流水线结构:取指、译码、执行、内存访问、写回。

● 取指阶段,访问指令Cache或者总线,获取指令,同时访问BTB,发起0延时跳转。

● 译码阶段,访问动态分支预测器和返回栈,发起分支的预测跳转,同时进行指令译码,读取寄存器堆,处理数据相关性和数据前馈。

● 执行阶段,完成单周期整型计算指令和多周期乘除法指令的执行、存储/加载指令地址计算和跳转指令处理。其中,整型计算包括普通的算术指令和逻辑指令。

● 内存访问阶段,利用执行阶段产生的存储/载入指令的目标地址访问数据Cache或者总线。

● 写回阶段,将指令执行结果写回寄存器堆。

可配置的物理内存保护单元(Physical Memory Protection,PMP)负责物理地址的权限检查,实现内存的保护功能。权限可划分为:不可读写/只读/可读写,可执行/不可执行。

调试单元支持各种调试方式,包括软件断点、内存断点、单步和多步的指令跟踪等,可在线调试CPU、通用寄存器(GPR)、控制寄存器(CSR)和内存。

E906设计有片上紧耦合的IP接口和多条AHB-Lite的总线接口。片上紧耦合的IP接口集成矢量中断控制器(CLIC),支持中断嵌套。外部中断源数量最高可配置240个,中断优先级支持4/8/16/32级可配置。

3) 计算增强型微控制器:E907

a) 概述

玄铁E907采用5级按序流水线,典型工作频率>1GHz,是玄铁MCU处理器中的性能最高的处理器核,可选配高性能浮点以及DSP计算单元,同时支持TCM扩展以及中断加速技术以进一步提升实时性。可以应用在语音入口MCU、TWS、MPU、多模无线接入等场景。

E907处理器体系结构的主要特点如下:

b)处理器简介

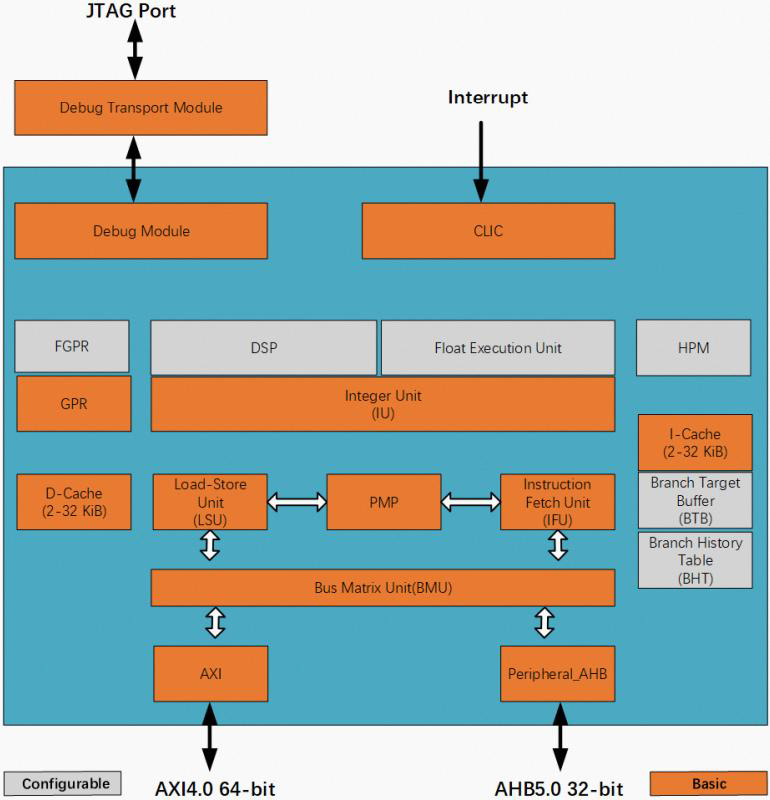

E907的结构框图如下所示:

E907处理器采用5级流水线结构:取指、译码、执行、内存访问、写回。

● 取指阶段,访问指令Cache或者外部总线,获取指令,同时访问BTB,发起0延时跳转。

● 译码阶段,访问动态分支预测器和返回栈,发起分支的预测跳转,同时进行指令译码,读取寄存器堆,处理数据相关性和数据前馈。

● 执行阶段,完成单周期整型计算指令和多周期乘除法指令的执行、存储/加载指令地址计算和跳转指令处理。其中,整型计算包括普通的算术指令和逻辑指令。

● 内存访问阶段,利用执行阶段产生的存储/载入指令的目标地址访问数据Cache或者外部总线。

● 写回阶段,将指令执行结果写回寄存器堆。

可配置的物理内存保护单元(Physical Memory Protection,PMP)负责物理地址的权限检查实现内存的保护功能,权限可划分为:不可读写/只读/可读写,可执行/不可执行。

调试单元(Debug Module,以下简称DM)支持各种调试方式,包括软件断点、内存断点、单步和多步的指令跟踪等多种方式,可在线调试CPU、通用寄存器(GPR)、控制寄存器(CSR)和内存。

E907设计有片上紧耦合的IP接口和两条主设备总线接口。片上紧耦合的IP接口集成矢量中断控制器(CLIC),支持中断嵌套。外部中断源数量最高可配置240个,中断优先级支持4/8/16/32级可配置。