4P3040.00-490 用于提供与并行总线相同逻辑功能

一个公共汽车1是一个通信系统数据中的组件之间计算机,或计算机之间。这个表达涵盖了所有相关的五金器具组件(电线、光纤等。)和软件,包括通信协议。[3]

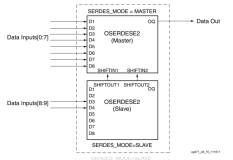

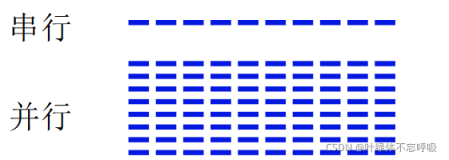

早期的计算机总线是具有多个硬件连接的并行电线,但该术语现在用于提供与并行总线相同逻辑功能的任何物理配置电气母线。现代计算机总线可以使用这两者平行的和比特串行连接,可以有线连接多站(电气并联)或雏菊花环拓扑结构,或通过交换集线器连接,如通用串行总线(USB)。

B&R ECE161-0

B&R ECE243-0

B&R ECEP128-0

B&R ECNT43-0

B&R ECPA81-2

B&R ECPE82-2

B&R ECPE84-2

B&R ECPNC3-1 11150168481

B&R ECPP40-01

B&R ECPP60-01

B&R HCMARC-0CT

B&R HCMCO3MC-1A

B&R MCGE31-0

B&R MDA115-0

B&R X20BM15

B&R ECR165

B&R 5CFCRD.0064-03

B&R X20CP1486

B&R 4P3040.00-490

B&R DO135

B&R AT664

B&R AO352

B&R 5AP1130.156C-000

B&R 7AO352.70

B&R 7DO138.70

B&R 7DI140.70

B&R 7DO135.70

B&R 7AI261.7

B&R 5AP920.1505-01

B&R 8AC120.60-1

B&R 8AC110.60-2

B&R 2AO300.6

B&R 7EX470.50-1