1.算法仿真效果

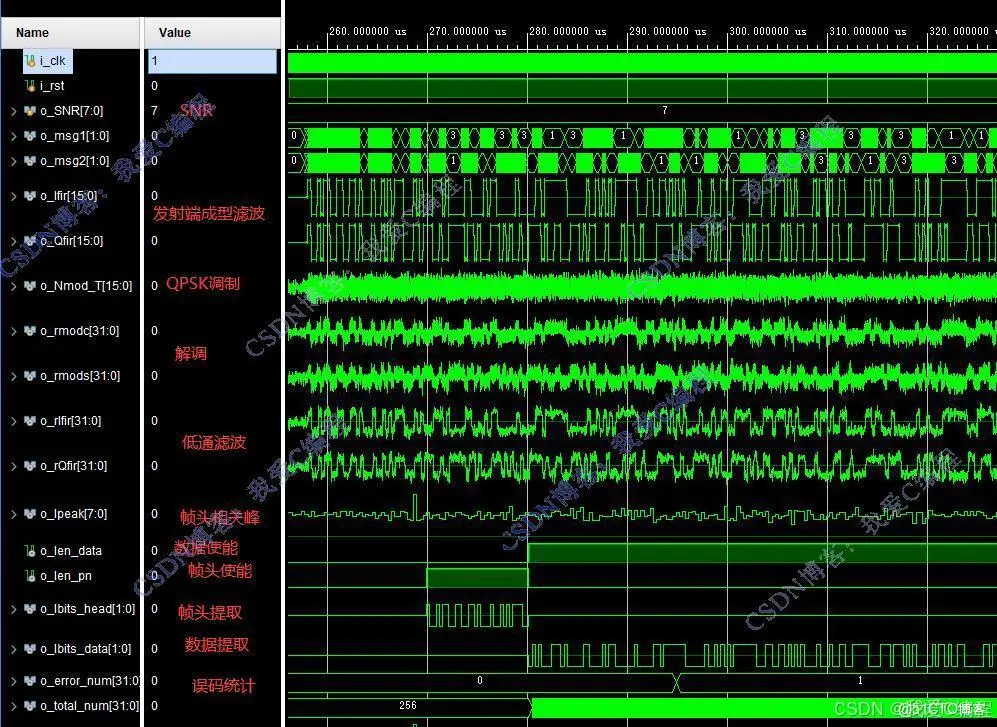

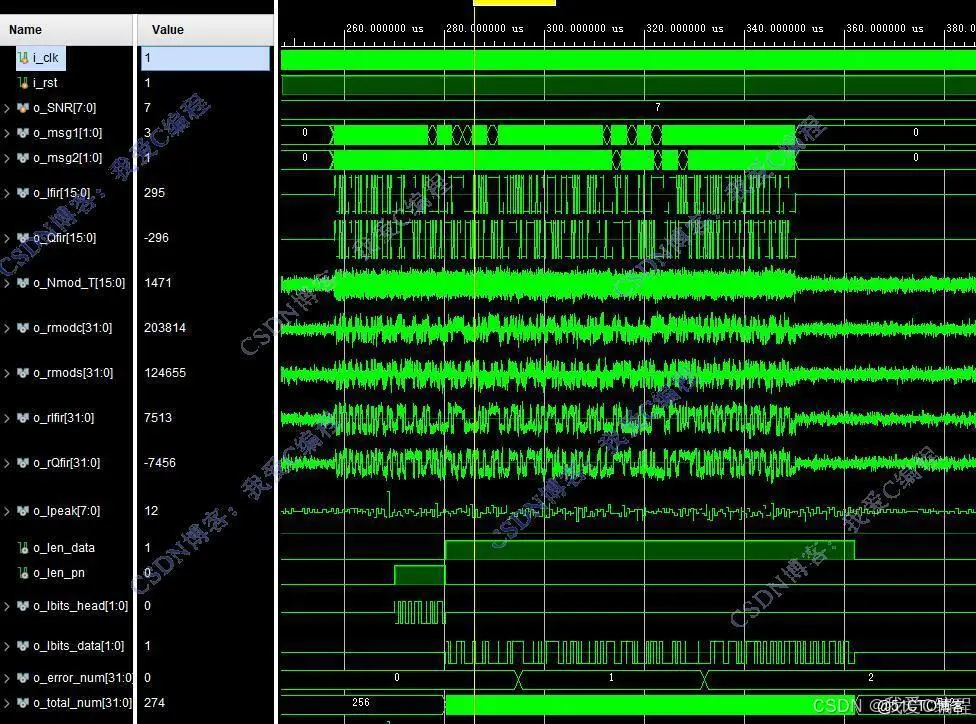

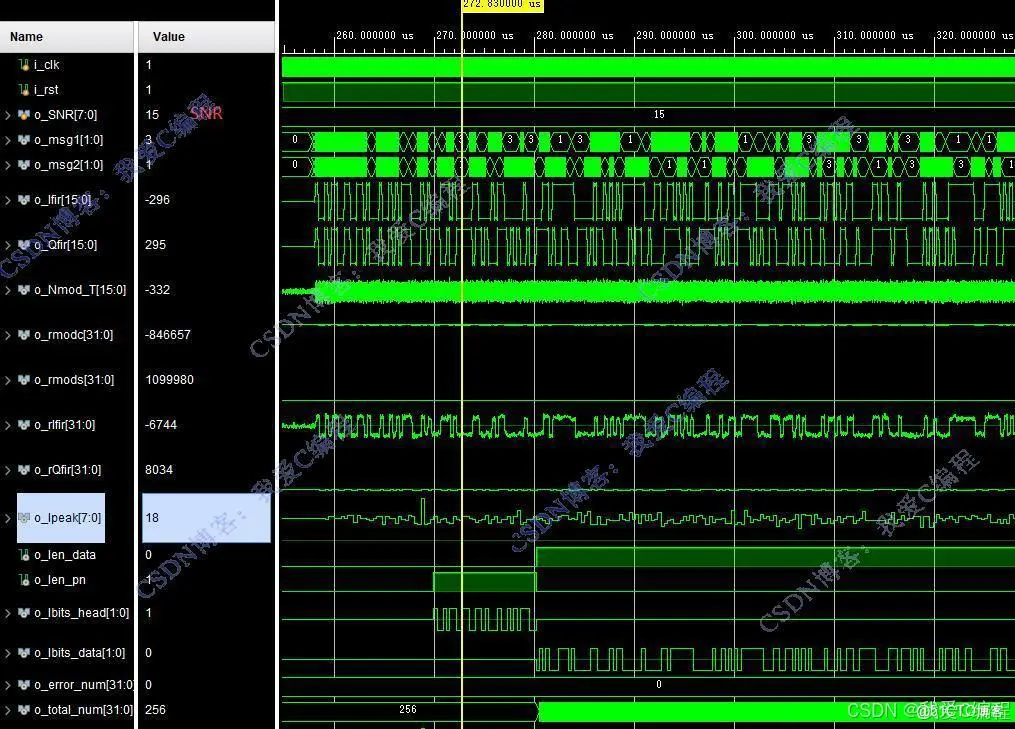

vivado2019.2仿真结果如下(完整代码运行后无水印):

系统包括QPSK调制模块,QPSK软解调模块,AWGN信道模块,误码统计模块,帧同步模块,数据源模块等。

设置SNR=7db

缩小上面的波形,看完整的一帧波形,如下图所示:

设置SNR=15db

仿真操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

2.1QPSK

QPSK是一种数字调制方式,它将两个二进制比特映射到一个符号上,使得每个符号代表四种可能的相位状态。因此,QPSK调制解调系统可以实现更高的传输速率和更高的频谱效率。基于FPGA的QPSK调制解调系统通常由以下几个模块组成:

数据生成模块:生成要传输的二进制数据流。

QPSK调制模块:将二进制数据流转换为符号序列,并将每个符号映射到特定的相位状态。

QPSK解调模块:将接收到的符号序列解调为二进制数据流。

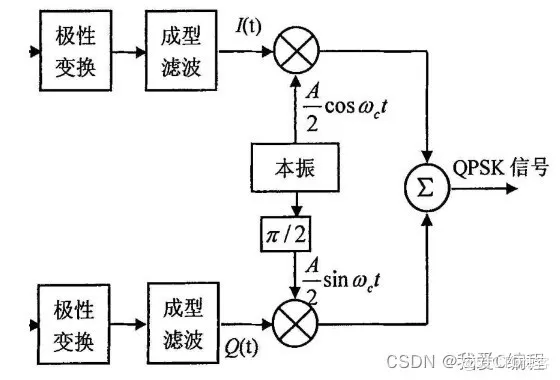

QPSK调制模块

QPSK调制模块将二进制数据流转换为符号序列,并将每个符号映射到特定的相位状态。QPSK调制使用四个相位状态,分别为0度、90度、180度和270度。在QPSK调制中,每个符号代表两个比特,因此,输入二进制数据流的速率必须是符号速率的两倍。

QPSK调制模块通常使用带有正弦和余弦输出的正交调制器(I/Q调制器)来实现。在I/Q调制器中,输入信号被分成两路,一路被称为“正交(I)路”,另一路被称为“正交(Q)路”。每个输入符号被映射到一个特定的正交信号,然后通过合成器将两个信号相加,形成QPSK调制信号。

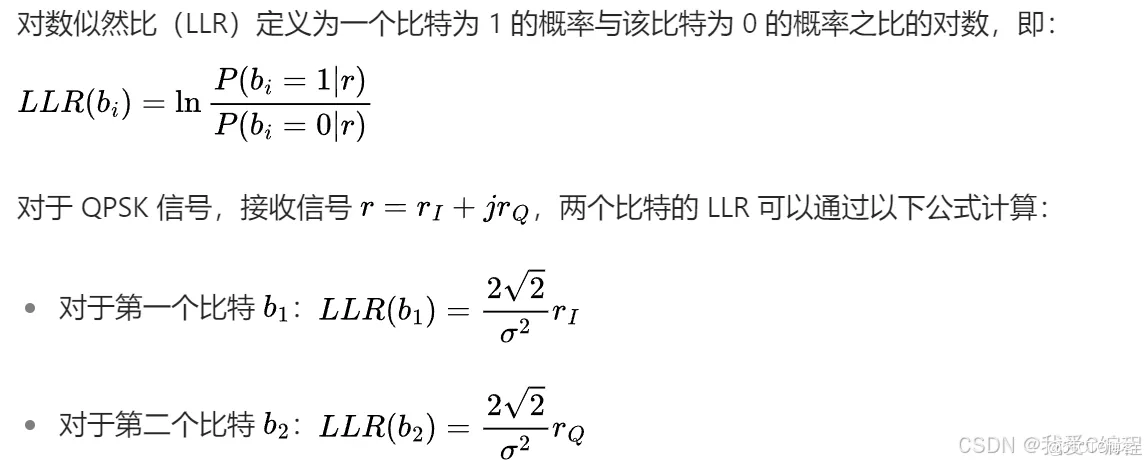

QPSK软解调模块

软解调是QPSK软解调的关键步骤,它利用判决符号和相位估计的结果进行概率估计,以提高解调的准确性。假设判决符号为d_hat,软解调过程的结果为软解调符号d。常见的软解调公式为:

该概率可以通过估计信号点的概率分布函数或使用最大似然估计等方法得到。软解调过程需要进行概率估计,以提高解调的准确性。这涉及到估计信号点的概率分布函数或使用其他概率估计方法,其中噪声的影响需要被适当地考虑。

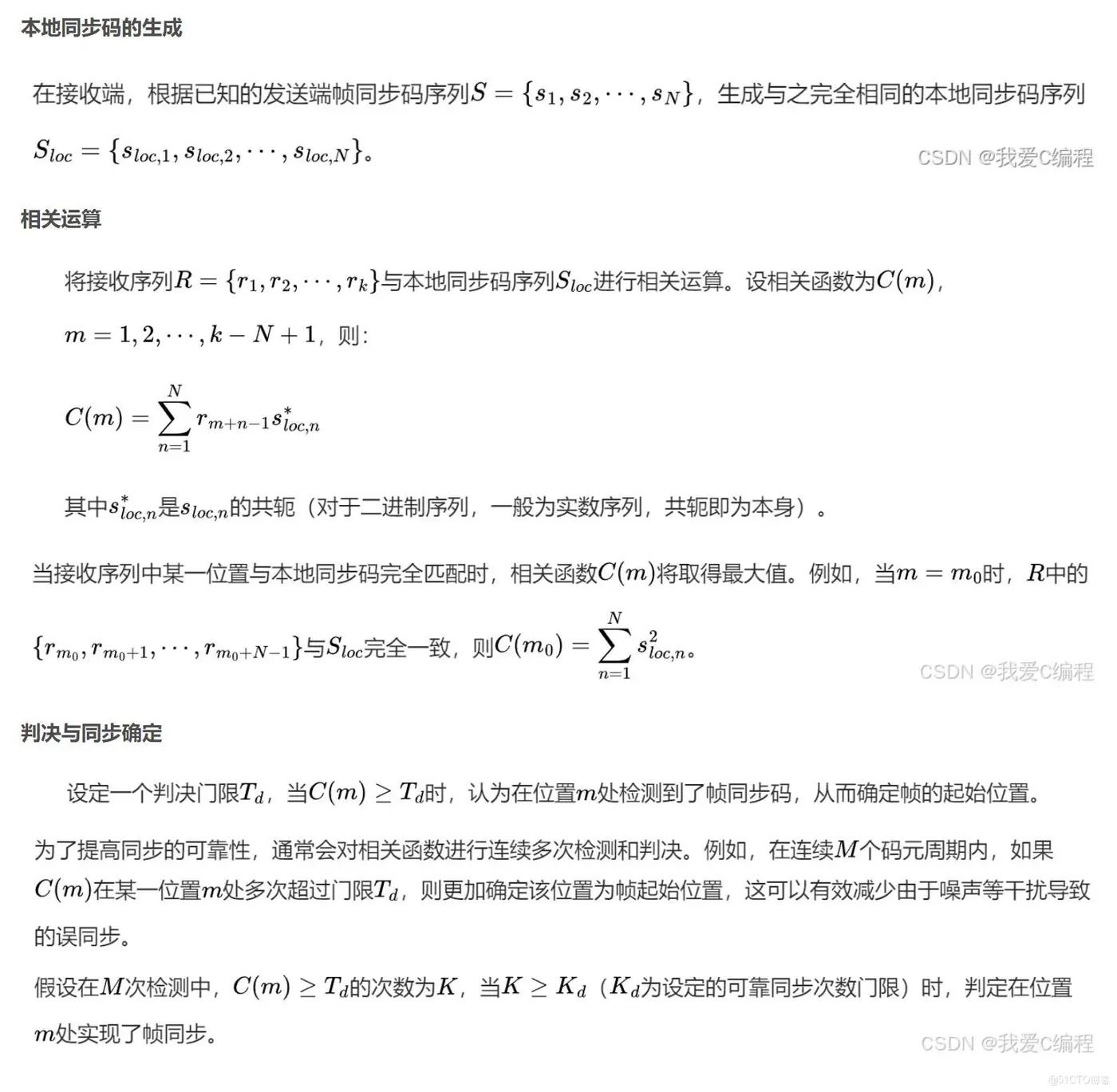

2.2 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.Verilog核心程序

TQPSK TQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Ibits(i_Ibits),

.i_Qbits(i_Qbits),

.o_Ifir (o_Ifir),

.o_Qfir (o_Qfir),

.o_cos (),

.o_sin (),

.o_modc (),

.o_mods (),

.o_mod (o_mod_T)

);

//加入信道

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_mod_T[24:9] + o_mod_T[25:10]),

.o_noise(),

.o_dout(o_Nmod_T)

);

//QPSK解调

RQPSK RQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_med (o_Nmod_T),

.o_cos (),

.o_sin (),

.o_modc (o_rmodc),

.o_mods (o_rmods),

.o_Ifir (o_rIfir),

.o_Qfir (o_rQfir),

.o_Ibits(),

.o_Qbits(),

.o_Ibits_data(o_Ibits_data),

.o_Ibits_head(o_Ibits_head),

.o_Ipeak(o_Ipeak),

.o_Ien_data(o_Ien_data),

.o_Ien_pn(o_Ien_pn),

.o_Iframe_start(o_Iframe_start),

.o_Qbits_data(o_Qbits_data),

.o_Qbits_head(o_Qbits_head),

.o_Qpeak(o_Qpeak),

.o_Qen_data(o_Qen_data),

.o_Qen_pn(o_Qen_pn),

.o_Qframe_start(o_Qframe_start)

);

//计算误码率

//I,Q两路分别计算,最后统计平均值作为误码率

//error calculate

wire [31:0]w_error_num1;

wire [31:0]w_error_num2;

Error_Chech Error_Chech_u1(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans({i_Ibits}),

.i_en_data(o_Ien_data),

.i_rec(o_Ibits_data),

.o_error_num(w_error_num1),

.o_total_num(),

.o_rec2 ()

);

//error calculate

Error_Chech Error_Chech_u2(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans({i_Qbits}),

.i_en_data(o_Qen_data),

.i_rec(o_Qbits_data),

.o_error_num(w_error_num2),

.o_total_num(o_total_num),

.o_rec2 ()

);

assign o_error_num={w_error_num1[31],w_error_num1[31:1]} + {w_error_num2[31],w_error_num2[31:1]} ;

endmodule