文章目录

设计的功能描述(含所有实现的指令描述,以及单周期/流水线CPU频率)

单周期模块作用

流水线模块作用

流水线划分

设计的功能描述(含所有实现的指令描述,以及单周期/流水线CPU频率)

add:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后相加之后将结果写入目的寄存器中。

sub:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后相减之后将结果写入目的寄存器中。

and:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行与运算之后将结果写入目的寄存器中。

or:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行或运算之后将结果写入目的寄存器中。

xor:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行异或运算之后将结果写入目的寄存器中。

sll:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后将操作数1逻辑左移操作数2大小的位数之后将结果写入目的寄存器中。

srl:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后将操作数1逻辑右移操作数2大小的位数之后将结果写入目的寄存器中。

sra:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后将操作数1算术右移操作数2大小的位数之后将结果写入目的寄存器中。

addi:将指令中指明的一一个包含操作数的寄存器中的操作数读出,然后将该操作数与指令中指明的立即数相加之后将结果写入目的寄存器中。

andi:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数与指令中指明的立即数做与运算之后将结果写入目的寄存器中。

ori:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数与指令中指明的立即数做或运算之后将结果写入目的寄存器中。

xori:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数与指令中指明的立即数做异或运算之后将结果写入目的寄存器中。

slli:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数逻辑左移指令中指明的立即数的大小的位数之后将结果写入目的寄存器中。

srli:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数逻辑右移指令中指明的立即数的大小的位数之后将结果写入目的寄存器中。

srai:将指令中指明的一个包含操作数的寄存器中的操作数读出,然后将该操作数算术右移指令中指明的立即数的大小的位数之后将结果写入目的寄存器中。

lw:以指令中指明的包含操作数的寄存器中的操作数和指令中指明的立即数相加,然后读出以此相加结果为地址的存储单元的值,并将其写入目的寄存器中。

ialr:将指令中指明的包含操作数的寄存器中的操作数和指令中指明的立即数相加作为下一次PC的值,然后将当前PC的值加4之后得到的值写入目的寄存器中。

sw:以指令中指明的包含操作数的寄存器1中的操作数和指令中指明的立即数相加,然后将指令中指明的包含操作数的寄存器2中的操作数写入以此相加结果为地址的存储单元中。

beq:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行比较,若操作数1与操作数2相等,则将当前的PC地址加上指令中指明的立即数的结果作为下一次的PC的值,否则,就将当前的PC地址加上4的结果作为下一次的PC的值。

bne:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行比较,若操作数1与操作数2不相等,则将当前的PC地址加上指令中指明的立即数的结果作为下一次的PC的值,否则,就将当前的PC地址加上4的结果作为下一次的PC的值。

blt:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行有符号比较,若操作数1小于操作数2,则将当前的PC地址加上指令中指明的立即数的结果作为下一次的PC的值,否则,就将当前的PC地址加上4的结果作为下一次的PC的值。

bge:将指令中指明的两个包含操作数的寄存器中的操作数读出,然后进行有符号比较,若操作数1大于或等于操作数2,则将当前的PC地址加上指令中指明的立即数的结果作为下一次的PC的值,否则,就将当前的PC地址加上4的结果作为下一次的PC的值。

lui:将指令中指明的立即数做符号拓展成32位之后的结果写入目的寄存器中。

jal:将当前PC的值和指令中指明的立即数相加作为下一次PC的值,然后将当前PC的值加4之后得到的值写入目的寄存器中。

单周期CPU频率25MHz

流水线CPU频率90MHz

单周期模块作用

PC:将下一条指令的地址值传到imem模块。

Next. _pc:得到下一-次的pc值并传到PC模块。

imem:存储指令的模块。

decoder:译码单元,将输入的指令拆分,得到相应的操作数或是符号拓展后立即数,供后面的模块使用。

control:通过输入的指令得到相应的各个控制信号取值并输出到其他模块。

execute:将相应的操作数进行对应的计算得到结果并输出到需用的模块。

dram:存储单元。

compare:进行比较指令的比较操作,并输出决定是否跳转的信号。

流水线模块作用

PC:将下一条指令的地址值传到irom模块。

Next_pc:得到下一次的pc值并传到PC模块。

irom:存储指令的模块。

jump_ test:检测是否是跳转指令,并决定是否暂停。

IF_ID_ reg: 将IF阶段的部分信号传到ID阶段。

decoder:译码单元,将输入的指令拆分,得到相应的操作数或是符号拓展后立即数,供后面的模块使用。

control:通过输入的指令得到相应的各个控制信号取值并输出到其他模块。

conf_ test:冲突的检测模块,检测是否出现数据冲突,并输出相应的冲突信号以及发生冲突后应该从寄存器中读出的正确值。

ID_ EX_ reg: 将ID阶段的部分信号传到EX阶段。

execute:将相应的操作数进行对应的计算得到结果并输出到需用的模块。

compare:进行比较指令的比较操作,并输出决定是否跳转的信号。

EX_MEM_reg:将EX阶段的部分信号传到MEM阶段。

dram:存储单元。

MEM_WB._reg:将MEM阶段的部分信号传到WB阶段。

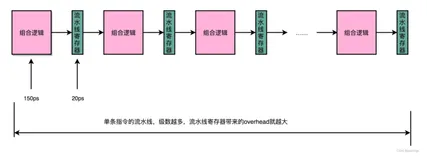

流水线划分

IF阶段:完成下一次pc取值的计算,并根据当前pc值把相应指令从irom模块中取出然后输出到后续的阶段;再者还有对跳转指令的检测,决定是否暂停。

ID阶段:接收IF阶段取得的指令,然后将指令中的有效信息提取出来,例如I型指令的立即数符号拓展值、R型指令的操作数等等,并得到各个控制信号的取值然后输出到后续的模块,再者检测是否出现数据冲突,并进行相应的处理。

EX阶段:接收ID阶段传来的一些控制信号和相应的操作数,并据此进行相应的计算或比较操作,得到结果后输出到MEM阶段。

MEM阶段:对DRAM进行读或写的操作。

WB阶段:将前面阶段得到的数据根据控制信号选择之后写入相应的寄存器中。