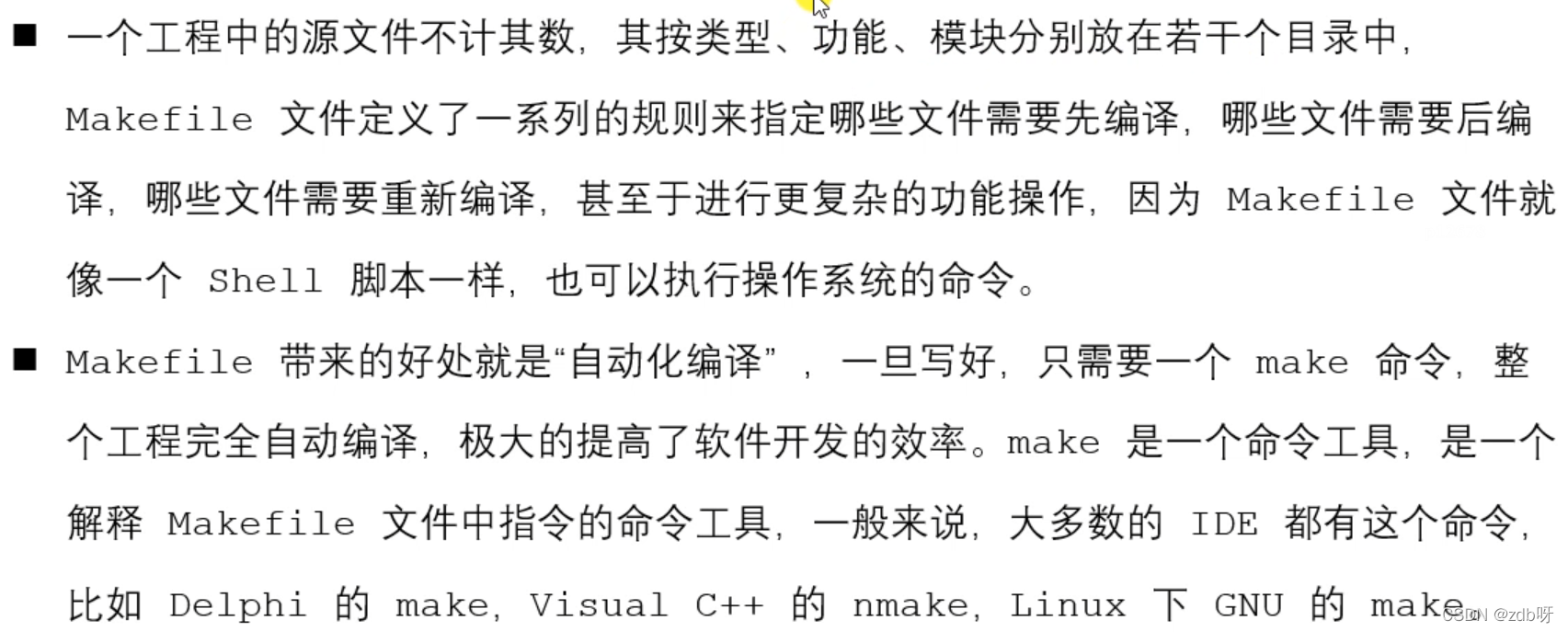

01 什么是Makefile

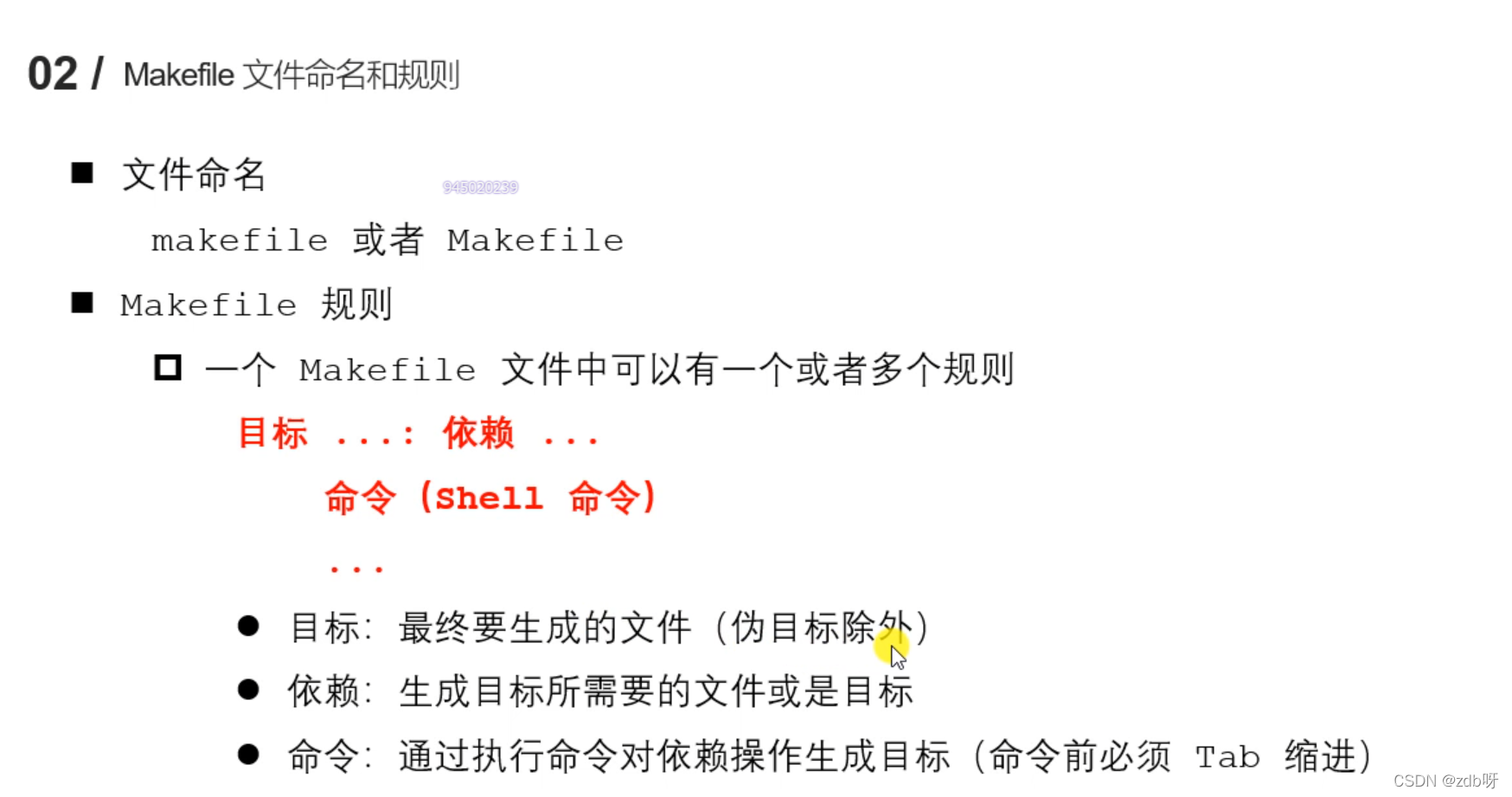

02 Makefile规则

版本一

app:sub.c add.c mult.c div.c main.c gcc sub.c add.c mult.c div.c main.c -o app

版本二

app:sub.o add.o mult.o div.o main.o gcc sub.o add.o mult.o div.o main.o -o app sub.o:sub.c gcc -c sub.c -o sub.o add.o:add.c gcc -c add.c -o add.o mult.o:mult.c gcc -c mult.c -o mult.o div.o:div.c gcc -c div.c -o div.o main.o:main.c gcc -c main.c -o main.o

第二个版本编写更麻烦,但是更新依赖文件的时候,不需要全部重新编译

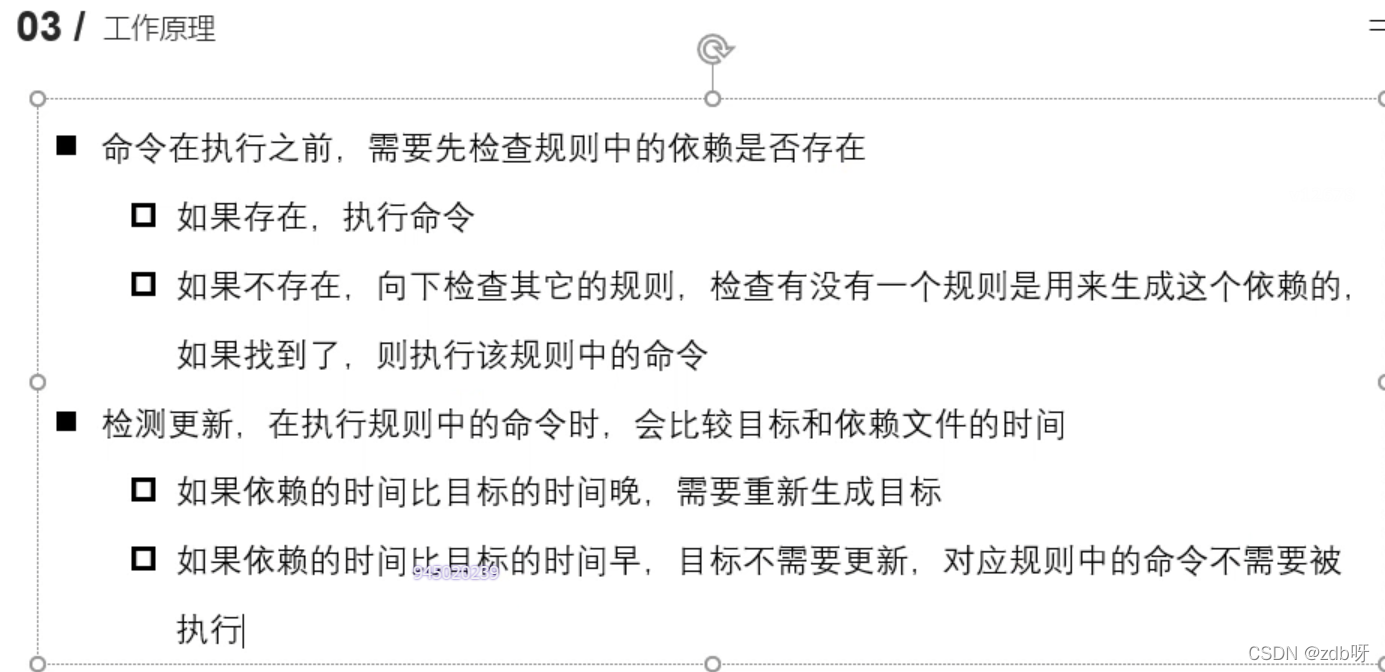

03 工作原理

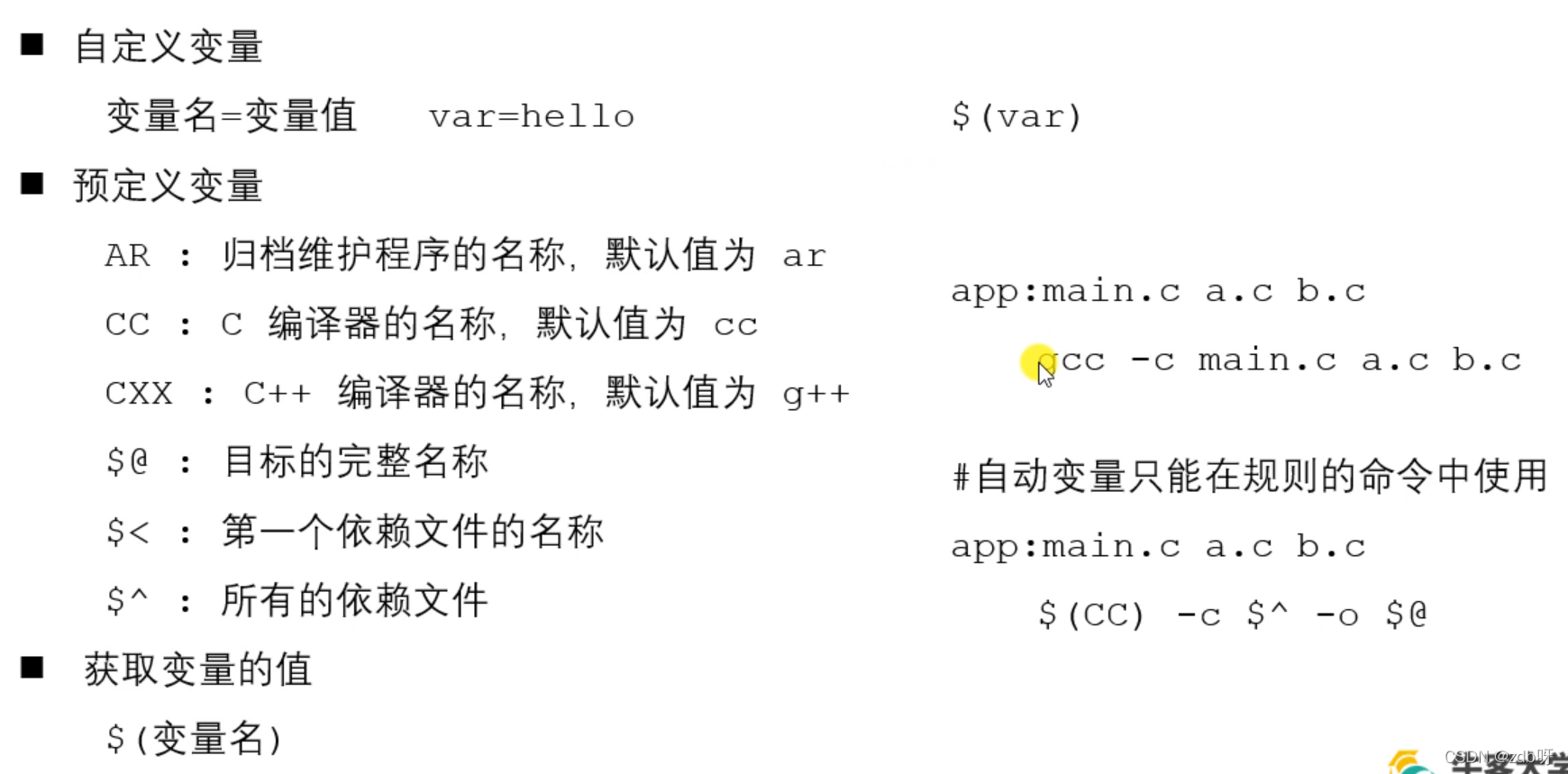

04 变量

#定义变量 src=sub.o add.o mult.o div.o main.o target=app $(target):$(src) $(CC) $(src) -o $(target) sub.o:sub.c gcc -c sub.c -o sub.o add.o:add.c gcc -c add.c -o add.o mult.o:mult.c gcc -c mult.c -o mult.o div.o:div.c gcc -c div.c -o div.o main.o:main.c gcc -c main.c -o main.o

有什么用:简化代码

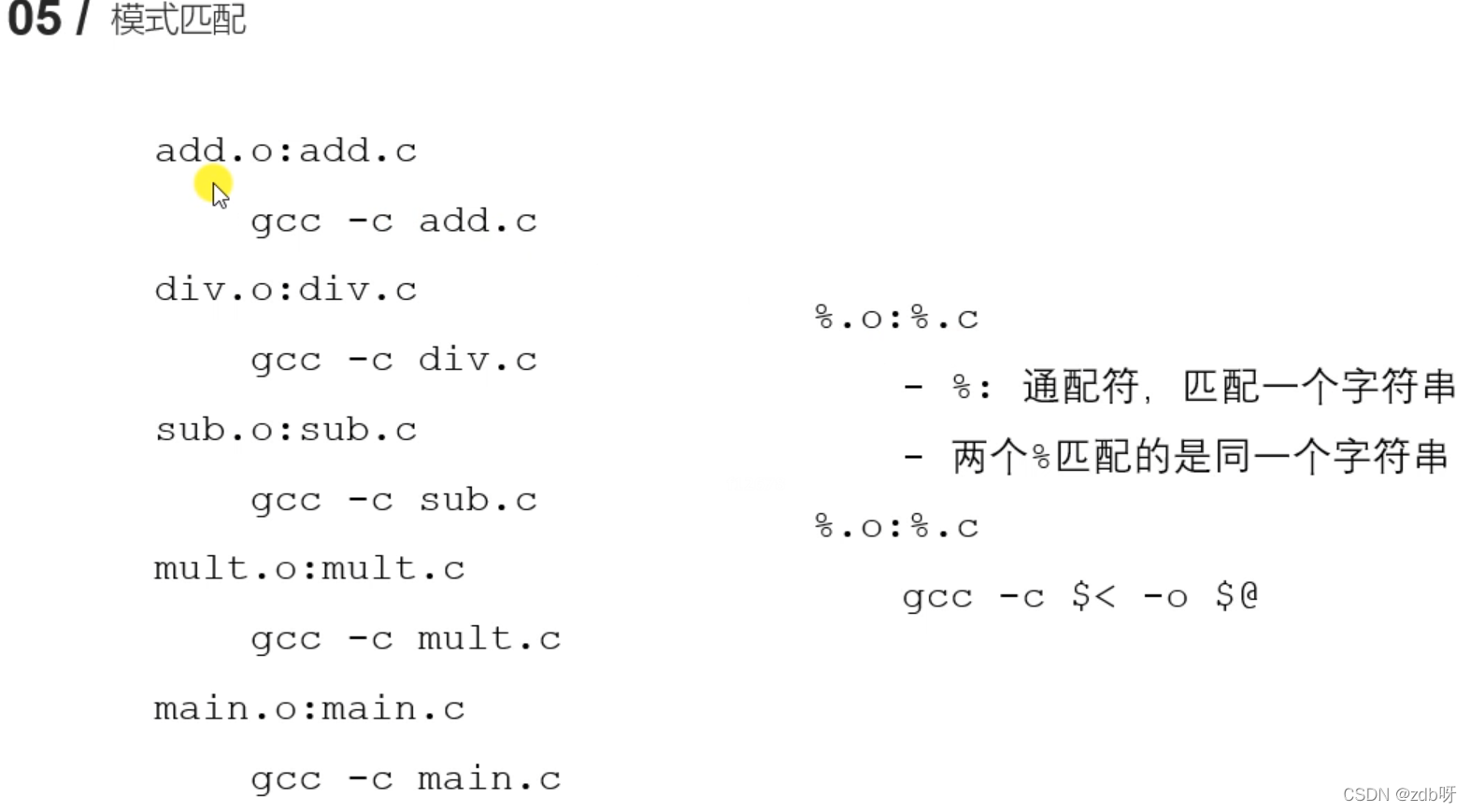

05 模式匹配

再次优化

#定义变量 src=sub.o add.o mult.o div.o main.o target=app $(target):$(src) $(CC) $(src) -o $(target) %.o:%.c $(CC) -c $< -o $@

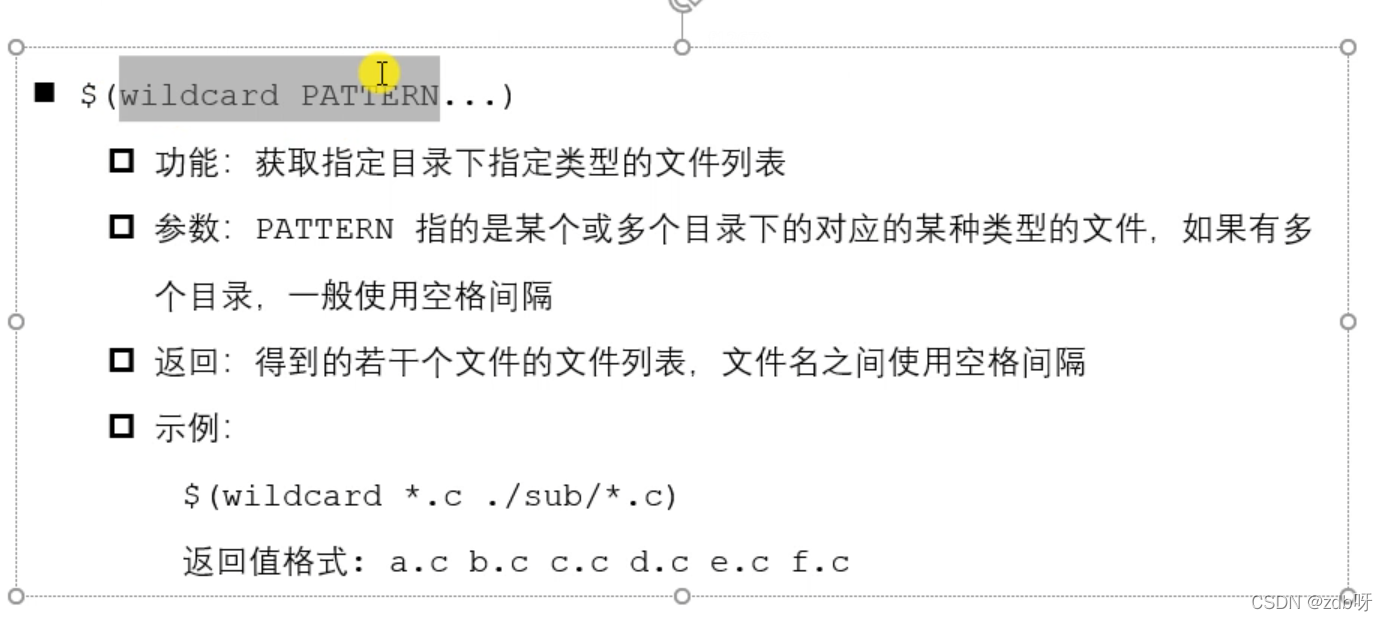

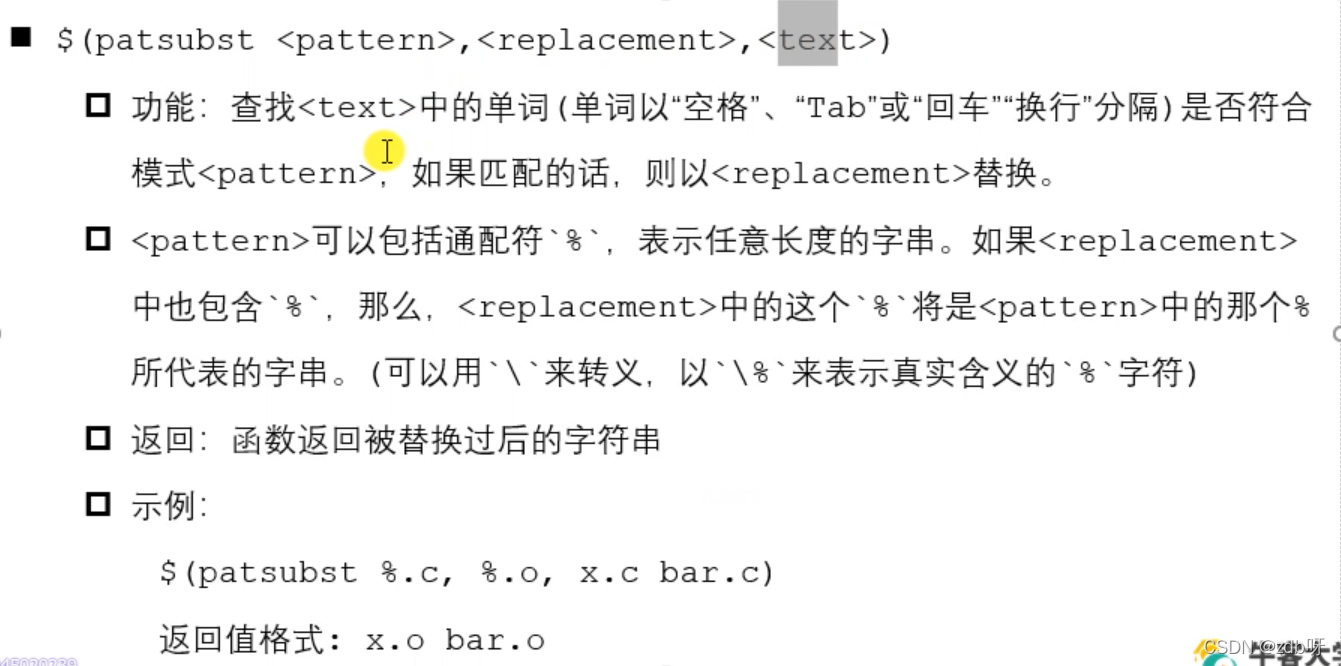

06 函数

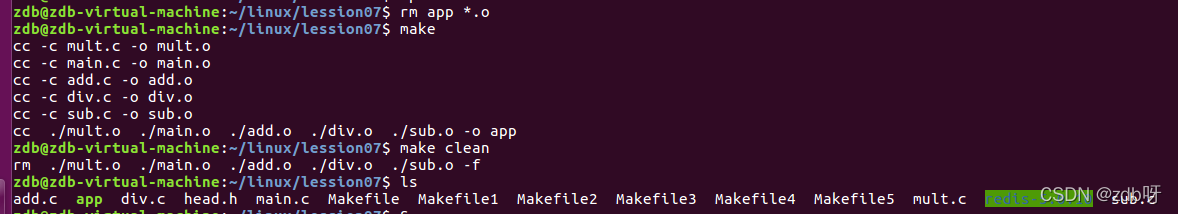

#定义变量 # add sub.o add.o mult.o div.o main.o src=$(wildcard ./*.c) objs=$(patsubst %.c, %.o, $(src)) target=app $(target):$(objs) $(CC) $(objs) -o $(target) %.o:%.c $(CC) -c $< -o $@

#定义变量 # add sub.o add.o mult.o div.o main.o src=$(wildcard ./*.c) objs=$(patsubst %.c, %.o, $(src)) target=app $(target):$(objs) $(CC) $(objs) -o $(target) %.o:%.c $(CC) -c $< -o $@ #删除.o中间文件 .PHONY:clean #指定不会生成文件 clean: rm $(objs) -f