Quartus ii

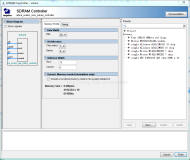

Error (170040): Can't place all RAM cells in design

Info (170034):Selected device has 46 memory locations of type M9K. The current designrequires 55 memory locations of type M9K to successfully fit. Info (170033):Memory usage required for the design in the current device: 120% M9K memoryblock locations required 复制代码

Error (171000): Can't fit design in device

Error: Quartus II 64-Bit Fitter was unsuccessful. 2 errors,67 warnings

Error: Peakvirtual memory: 882 megabytes Error: Processingended: Wed Mar 01 11:24:58 2017 Error: Elapsedtime: 00:00:11 Error: Total CPUtime (on all processors): 00:00:11 复制代码

Error (293001): Quartus II Full Compilation was unsuccessful.4 errors, 112 warnings

原因片上ram分配的太多了,fpga资源不够

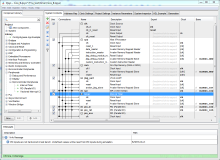

Description Resource Path Location Type

region `onchip_memory2' overflowed by 5808 bytes RGLV5KSoftware C/C++ Problem

原因 ram资源不够。

Description Resource Path Location Type

undefined reference to `__alt_invalid' alt_sys_init.c /RGLV5KSoftware_bsp C/C++Problem

nios中偶尔出现了这个错误,后发现dsp文件的配置有错误,

在dsp文件右击,选择niosii---dsp editor

打开的dsp edit偶尔选项卡中,在前面三项都选择jtag_uart

再次编译工程,不会报错。

打开APP工程内的Makefile,寻找C_SRCS关键字,没有的话自己手动加入。

然后在后面添加错误的文件

C_SRCS += src/debug/debug.c

Error (12153): Can't elaborate top-leveluser hierarchy

Quartus II不能精细的顶级用户层次结构

实体名字与你的工程名不一致

Description Resource Path Location Type

address 0x17fa0 of RGLVPulseSoftware.elfsection .rwdata' is not within region onchip_memory2' RGLVPulseSoftware C/C++ Problem

address 0x19e84 of RGLVPulseSoftware.elfsection .onchip_memory2' is not within region onchip_memory2'C/C++ Problem

也是片上ram空间不够引起的。

nios ii SEVERE System ID mismatch -connected 0x1001703a, expected 0x0.

原因一

nios ide/sdk使用的sopcinfo或者ptf文件和你对fpga配置的文件不是同一个工程建立的.

原因二

system id不正确。在qsys中删除systemid组件并重新添加,然后generate 解决

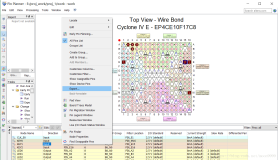

Error (176310): Can't place multiple pinsassigned to pin location Pin_6 (IOPAD_X0_Y22_N21)

Info(176311): Pin o_epcs_sdo is assigned to pin location Pin_6 (IOPAD_X0_Y22_N21) Info(176311): Pin ~ALTERA_ASDO_DATA1~ is assigned to pin location Pin_6(IOPAD_X0_Y22_N21) 复制代码

原因是不能分配给多功能管脚Pin_K22 。 这是由于Pin_K22 是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。如果要用它当普通IO,需要提前设置一下:assignments>device>deviceand pin options>dual-purpose pins里面把nCEO设置成use as regular i/o就可以了。

8

Error: Can't place 108 pins with 2.5 V I/Ostandard because Fitter has only 81 such free pins available for generalpurpose I/O placement.

为了避免以上情况的出现,常常使用Virtual Pin对非IO引脚的信号进行约束,经过约束的信号,综合布线器将不对其分配IO资源。

具体方法如下:

在Quartus II中Assignments->AssignmentEditor,在Category栏选择logicoptions,到列表中To列下添加要设置的引脚接口,将AssignmentName设置为Virtual Pin,将Value设置为On,Enabled 设置为Yes,如果需要设置的很多,可以通过在Pin Planner中将引脚复制过来。

这样设置为Virtual Pin 就不会占用FPGA的IO资源,而且时序仿真不会增加额外的延时,更加准确。

2、用quartus设计框图时出现错误,错误信息如下:

Error: Can't place 117 pins with LVTTLI/O standard because Fitter has only 85 such free pins available for generalpurpose I/O placement

Error: Can't place pins due to device constraints

Error: Can't fit design in device

Error: Quartus II Fitter wasunsuccessful. 3 errors, 0 warnings

Error: Quartus II Full Compilation wasunsuccessful. 3 errors, 0 warnings

这个问题我也碰到过,不到10分钟就解决了。

解决方法:

在你开发的时候,你在给芯片指定管脚的时候, 可能因为某些原因删除了一些管脚, 而你在ALL PIN列表中却没有删除,当你继续分配的时候,虽然你实际用到的管脚不到85,但是你曾经分配的管脚已经有117个了。 所以解决方法很简单,就是在ALLPIN列表中删除未用管脚。

感觉这是QuartsII的一个小bug。

Error: Can't place 98 pins with 3.3-VLVTTL I/O standard because Fitter has only 80 such free pins available forgeneral purpose I/O placement。

提示信息表明错误: 不能够放置98个3.3LVTTL I?O标准电平引脚,因为Fitter只能有80个空余的引脚用来作为GPIO。 请检查你的工程管理的器件,不能满足你的应用,得更换更多引脚或更高性能的芯片。