流水灯的简单设计

设计要求:低位点亮一个led,下一个周期,点亮两个led,逐次增加led的个数,全部点亮后的下一个周期,又点亮一个led

该实验需要两个模块,计数器模块和led控制模块

计数器模块:就是一个分频器,频率为2hz,系统时钟为50mhz,50_000_000/2=25_000_000,需要25位计数器。

Led控制模块:控制移位,到达全0时,led为全1。不断循环点亮。

顶层模块代码:

module ledwater(clk,rst_n,led);

input clk;

input rst_n;

output [7:0]led;

parameter MAX_CNT=24_999_999;

reg [24:0]cnt;//计数器

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt <=25'd0;

else if(cnt==MAX_CNT)

cnt <=25'd0;

else

cnt <=cnt + 1'b1;

reg [7:0]led_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

led_r <= 8'b1111_1111;

else if(cnt == MAX_CNT)begin

led_r <= led_r << 1;

if(led_r==8'd0)

led_r <= 8'b1111_1111;

// else

// led_r <= led_r;//此处不应该有,逻辑不对

end

else

led_r <= led_r;

assign led = led_r;

endmodule

测试文件只需设置clk和rst_n

代码:

`timescale 1ns/1ns

`define clk_period 20

module ledwater_tb;

reg clk;

reg rst_n;

wire [7:0]led;

ledwater

#(

.MAX_CNT(10)

)

ledwater0(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

initial clk=1;

always #(`clk_period/2)clk= ~clk;

initial begin

rst_n=0;

#(`clk_period*30+1);

rst_n=1;

end

endmodule

Ps:测试文件采用参数化设计

ledwater

#(

.MAX_CNT(10)

)

ledwater0(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

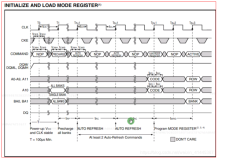

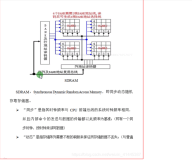

仿真波形: