16位全加器

通过该实验,学习元件例化。

1个16位全加器由4个4位全加器构成;

1个4位全加器由4个1位全加器构成;

1位全加器由两个半加器加上一个或门构成;

一个半加器由门级电路构成。

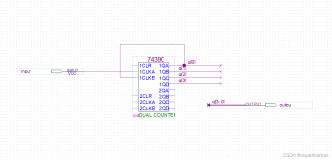

如下图:

顶层文件:

第二层:1个16位全加器由4个4位全加器构成;

第三层:1个4位全加器由4个1位全加器构成;

第四层:1位全加器由两个半加器加上一个或门构成;

第五层:一个半加器由门级电路构成

A |

B |

Sum |

C_out |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

代码部分:

顶层文件:

//16为全加器

//顶层文件为16为全加器

module add_full_16(a,b,c_in,sum,c_out);

input [15:0]a,b;

input c_in;

output [15:0]sum;

output c_out;

wire M0_c_out,M1_c_out,M2_c_out;

add_full_4 M0(.a(a[3:0]),.b(b[3:0]),.c_in(c_in),.sum(sum[3:0]),.c_out(M0_c_out));

add_full_4 M1(.a(a[7:4]),.b(b[7:4]),.c_in(M0_c_out),.sum(sum[7:4]),.c_out(M1_c_out));

add_full_4 M2(.a(a[11:8]),.b(b[11:8]),.c_in(M1_c_out),.sum(sum[11:8]),.c_out(M2_c_out));

add_full_4 M3(.a(a[15:12]),.b(b[15:12]),.c_in(M2_c_out),.sum(sum[15:12]),.c_out(c_out));

endmodule

第二层:

//4位全加器,4个4为全加器构成一个16位的全加器

module add_full_4(a,b,c_in,sum,c_out);

input [3:0]a,b;

input c_in;

output [3:0]sum;

output c_out;

wire B0_c_out,B1_c_out,B2_c_out;

add_full B0(.a(a[0]),.b(b[0]),.c_in(c_in),.sum(sum[0]),.c_out(B0_c_out));

add_full B1(.a(a[1]),.b(b[1]),.c_in(B0_c_out),.sum(sum[1]),.c_out(B1_c_out));

add_full B2(.a(a[2]),.b(b[2]),.c_in(B1_c_out),.sum(sum[2]),.c_out(B2_c_out));

add_full B3(.a(a[3]),.b(b[3]),.c_in(B2_c_out),.sum(sum[3]),.c_out(c_out));

endmodule

第三层:

//1位全加器

//4个1位全加器构成一个4位全加器

module add_full(a,b,c_in,sum,c_out);

input a,b;

input c_in;

output sum;

output c_out;

wire h0_sum,h0_c_out,h1_c_out;

add_half h0(.a(a),.b(b),.sum(h0_sum),.c_out(h0_c_out));

add_half h1(.a(c_in),.b(h0_sum),.sum(sum),.c_out(h1_c_out));

assign c_out = h0_c_out | h1_c_out;

endmodule

第四层:

//半加器

//两个半加器加上一个或门构成1位全加器

module add_half(a,b,sum,c_out);

input a,b;

output sum;

output c_out;

and u0(c_out ,a ,b);

xor u1(sum ,a ,b);

endmodule

前仿真代码:

`timescale 1ns/1ns

module add_full_16_tb;

reg [15:0]a,b;

reg c_in;

wire [15:0]sum;

wire c_out;

add_full_16 add_full_16(.a(a),.b(b),.sum(sum),.c_in(c_in),.c_out(c_out));

integer i;

initial begin

a = 0;b =0;c_in =0;

forever begin

for(i=0;i<65536;i=i+1)begin

#10 a = i;b = i;c_in = 0;

#10 a = i;b = i;c_in = 1;

end

end

end

endmodule

仿真图: