定时中断是一种在特定时间间隔触发的中断机制,常用于实时系统和需要周期性执行任务的应用中。以下是定时中断的基本结构:

一、硬件部分

- 定时器:这是产生定时中断的核心硬件组件。定时器可以是独立的芯片,也可以是微控制器或处理器内部的定时器模块。

- 时钟源:为定时器提供准确的时钟信号。时钟源可以是外部晶体振荡器、内部 RC 振荡器或其他时钟源。

- 中断控制器:负责接收定时器产生的中断信号,并将其转发给处理器。中断控制器可以是独立的芯片,也可以是微控制器或处理器内部的中断控制器模块。

二、软件部分

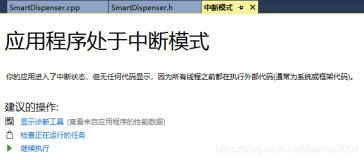

- 中断服务程序(ISR):当定时中断发生时,处理器会跳转到中断服务程序执行相应的任务。中断服务程序应该尽可能短小精悍,以减少中断响应时间。

- 主程序:在主程序中,需要初始化定时器和中断控制器,并设置定时中断的时间间隔。主程序还可以执行其他任务,等待定时中断的发生。

以下是一个简单的定时中断示例代码(以 C 语言为例):

展开过程

在实际应用中,定时中断的结构可能会更加复杂,需要考虑多个定时器的协同工作、中断优先级的设置、中断嵌套等问题。同时,为了提高系统的可靠性和稳定性,还需要进行错误处理和异常处理。