前言

本文节选UG471的第三章,进行整理翻译,用于介绍高级SelectIO逻辑资源内部的IO_FIFO资源。

IO_FIFO 概述

7系列器件在每个 I/O bank 中都有浅层 IN_FIFO 和 OUT_FIFO(统称为 IO_FIFO)。 尽管这些 IO_FIFO 是专门为内存应用设计的,但它们也可用作通用资源。 对于一般用途,所有输入和输出都通过互连路由。IO_FIFO 最常见的用途是与外部组件连接,作为 IOLOGIC 的扩展(例如,ISERDES 或 IDDR 和 OSERDES 或 ODDR)。 由于它们的通用互连能力,IO_FIFO 也可以用作额外的结构 FIFO 资源。

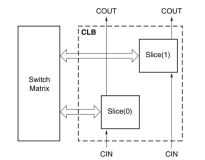

每个 I/O bank 包含四个 IO_FIFO,每个字节组一个 IO_FIFO。 一个字节组定义为一个 bank 内的 12 个 I/O。 IO_FIFO 与 I/O 字节组物理对齐。 当 IO_FIFO 用于连接 IOI 组件(例如输入和输出 SERDES 元素)时,这种对齐会产生最佳性能,这是它们最常见的用途。 但是,无论其位置如何,IO_FIFO 也可以与 FPGA 架构和其他 I/O bank 中的资源接口。 本节重点介绍使用 IO_FIFO 与 IOI 组件进行接口。

对于流入 FPGA 的外部数据,IN_FIFO 可以连接到 ILOGIC(例如,ISERDESE2、IDDR 或 IBUF)以接收传入数据并将其传递到结构。 对于流出 FPGA 的数据,OUT_FIFO 可以连接到 OLOGIC(例如 OSERDESE2、ODDR 或 OBUF)以将数据从结构传递并发送到 IOB。

IN_FIFO 从 ILOGIC 块接收 4 位数据,同时架构侧从阵列中读取 4 位或 8 位数据。 OUT_FIFO 从架构中接收 4 位或 8 位数据,而 OLOGIC 模块从阵列中读取 4 位数据。

每个 IO_FIFO 有一个 768 位的存储阵列,可以排列为 12 组 4 位数据或 10 组 8 位数据。 一个 IO_FIFO 有九个条目,包括一个输入和输出寄存器。 典型的 IO_FIFO 用途是作为两个频域之间交叉的并行 I/O 接口的缓冲区(例如,BUFR 域到/来自 BUFG 或 BUFH 域)或作为 2:1 串行器/解串器,将 PHY 与结构分离,以放宽结构性能要求。

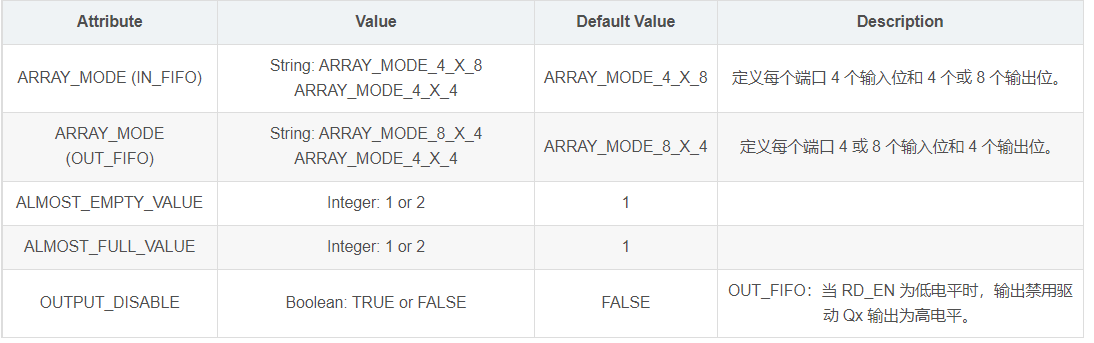

IO_FIFO 是常规 FIFO 的较浅版本,具有类似的功能。 IO_FIFO 的主要目的是支持 I/O 数据传输功能。 它们并非旨在取代内置 FIFO 或基于 LUT 的 FIFO。 IO_FIFO 支持标准标志逻辑、时钟和控制信号。 IO_FIFO 可以在两种模式下运行,4 x 4 模式 (1:1) 或 4 x 8/8 x 4 模式 (1:2/2:1)。

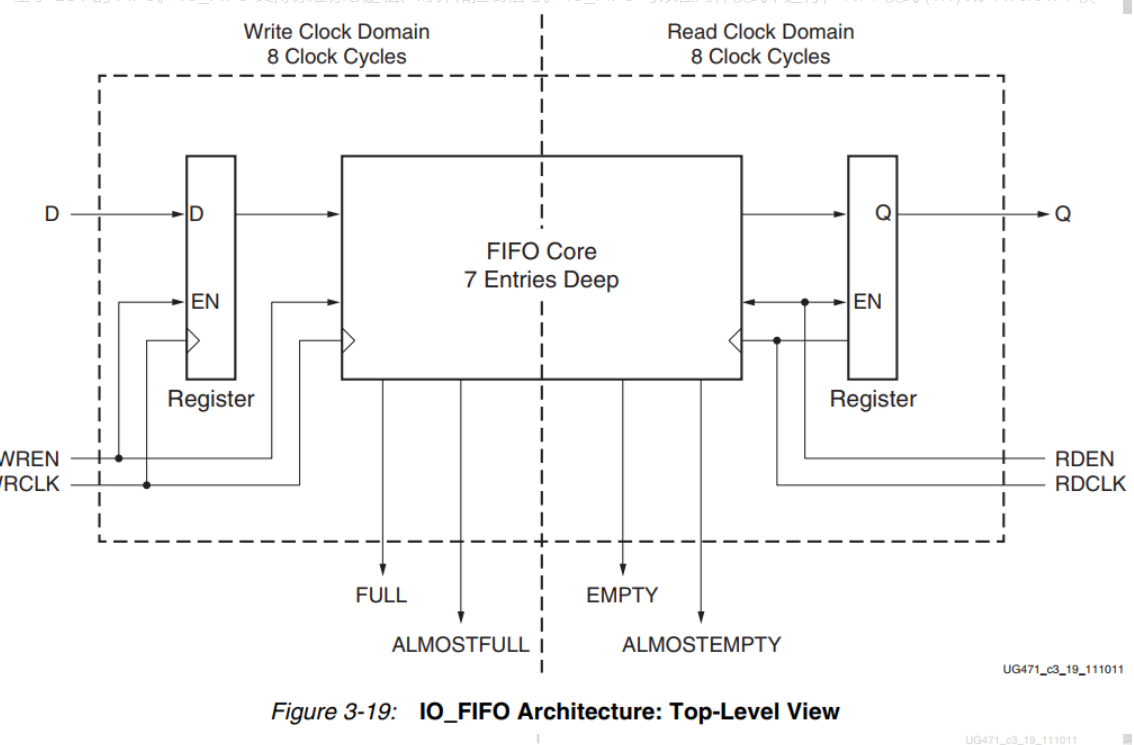

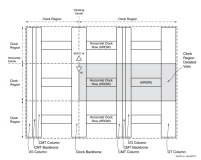

IO_FIFO 有一个输入寄存器、一个 7 入口深的 FIFO 内核和一个输出寄存器,如下图所示。 输入和输出寄存器是 IO_FIFO 的组成部分,为完整的 IO_FIFO 提供第八个存储位置。 寄存器、FIFO 内核和控制信号被视为单个原子单元。

IN_FIFO

IN_FIFO 在物理上与 I/O 字节组对齐以优化性能。 8 入口深 IN_FIFO 支持使用两种操作模式进行数据传输:

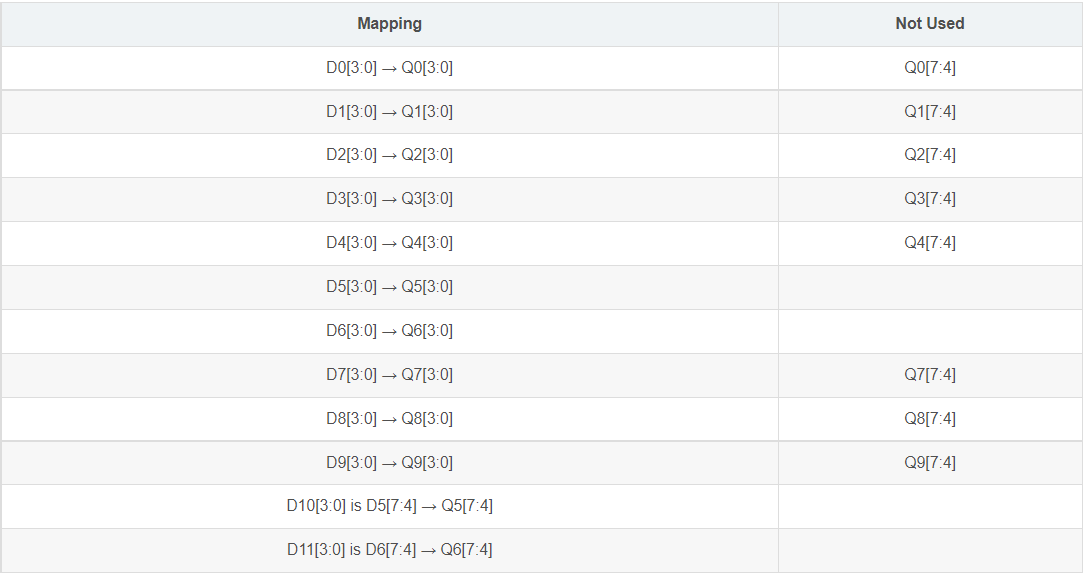

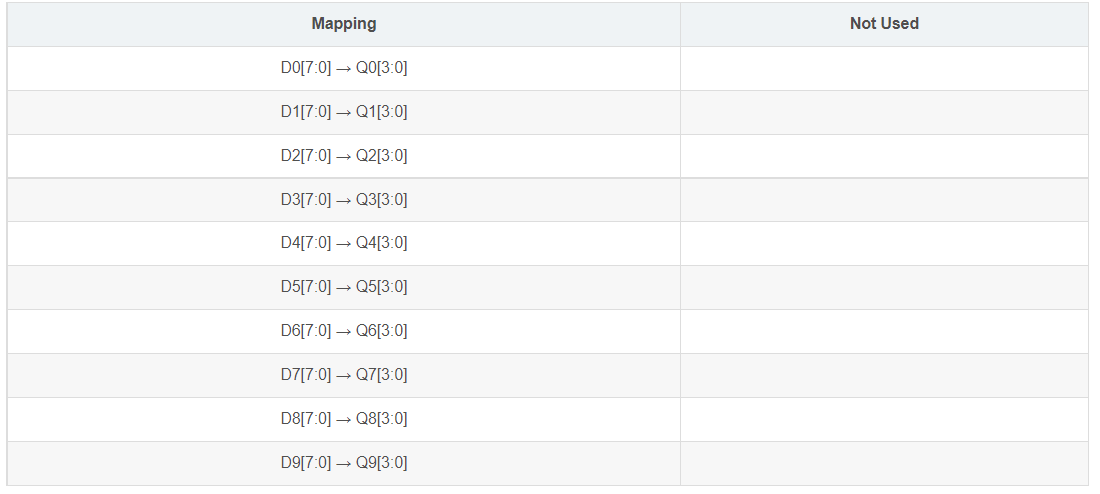

- 4 x 4 模式——该模式将 FIFO 配置为具有 12 个 4 位宽数据输入 (D) 和 12 个 4 位宽数据输出 (Q)。 D0[3:0] – D9[3:0] 端口映射到 Q0[3:0] – Q9[3:0] 端口。 D5[7:4] 和 D6[7:4] 是两个额外的数据输入端口 D10[3:0] 和 D11[3:0] 并映射到 Q5[7:4] 和 Q6[7:4] 额外的输出端口 Q10[3:0] 和 Q11[3:0]。不使用其他 Qn[7:4] 端口。 下表详细显示了 4 x 4 模式映射。

4 x 8 模式——该模式将 FIFO 配置为具有 10 个 4 位宽数据输入 (D) 和 10 个 8 位宽数据输出 (Q)。 在 4 x 8 模式下,4 位输入数据被解复用以形成 8 位输出数据宽度。 当输出时钟频率大于输入时钟频率的二分之一时,通常使用 4 x 8 模式,因此输出数据是输入数据宽度的两倍。 下表详细显示了 4 x 8 模式映射。

IN_FIFO 原语

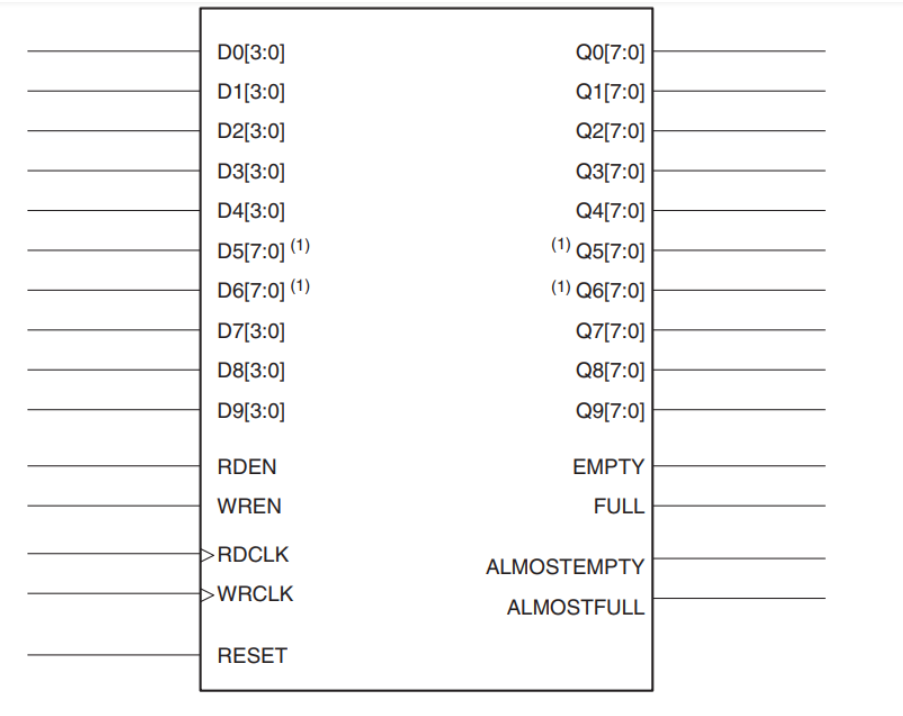

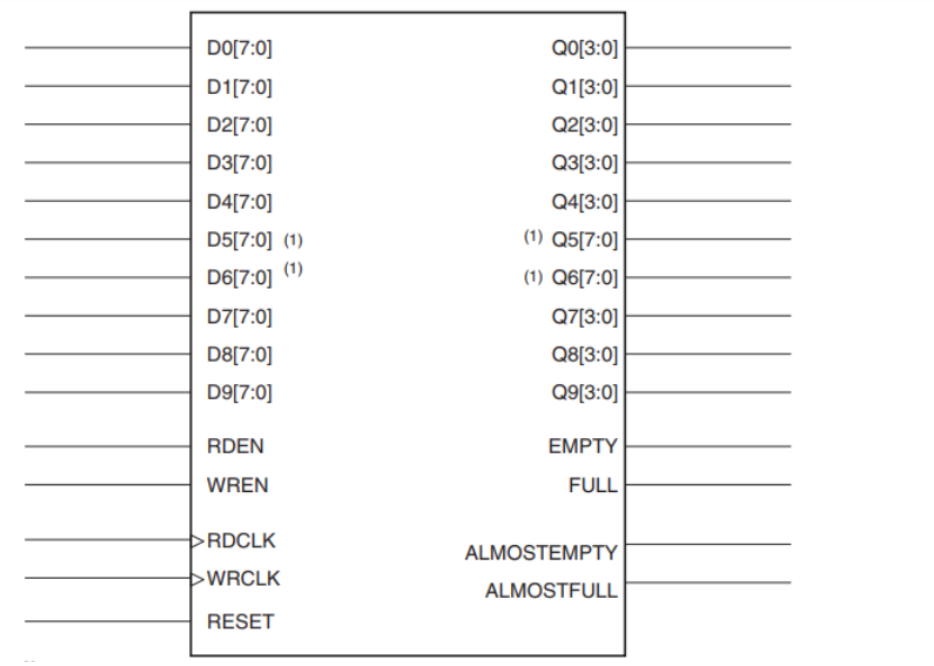

IN_FIFO 原语如下图所示。

4 x 4 模式下的额外输入端口 D10 (D5[7:4]) 和 D11 (D6[7:4]) 以及输出端口 Q10 (Q5[7:4]) 和 Q11 (Q5[7:4])。

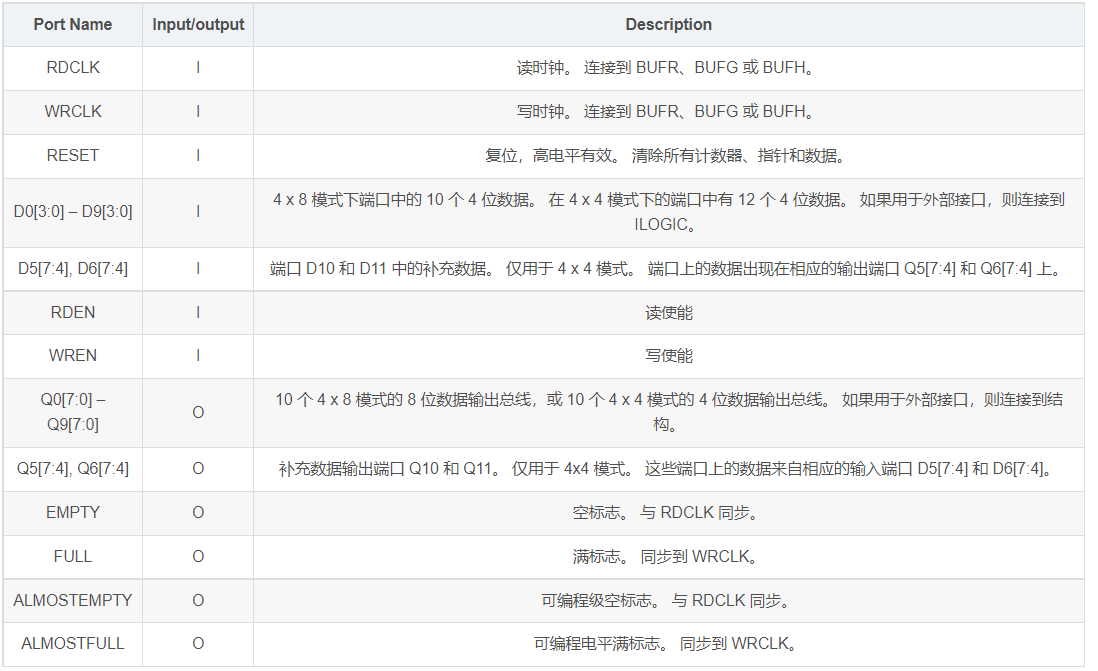

下表列出了 IN_FIFO 原语中的可用端口。

ALMOSTEMPTY、ALMOSTFULL相应的属性可以设置为值 1 或 2。 因此,在标志置位之后发生至少一或两次读取或写入。 由于 FIFO 的异步特性,可能会有一到两次额外的读取或写入,将读取或写入的总数增加到三到四次。

OUT_FIFO

OUT_FIFO 与 IN_FIFO 位于同一位置,并且在物理上与 I/O 字节组对齐以优化性能。 8 入口深 OUT_FIFO 支持使用两种操作模式进行数据传输:

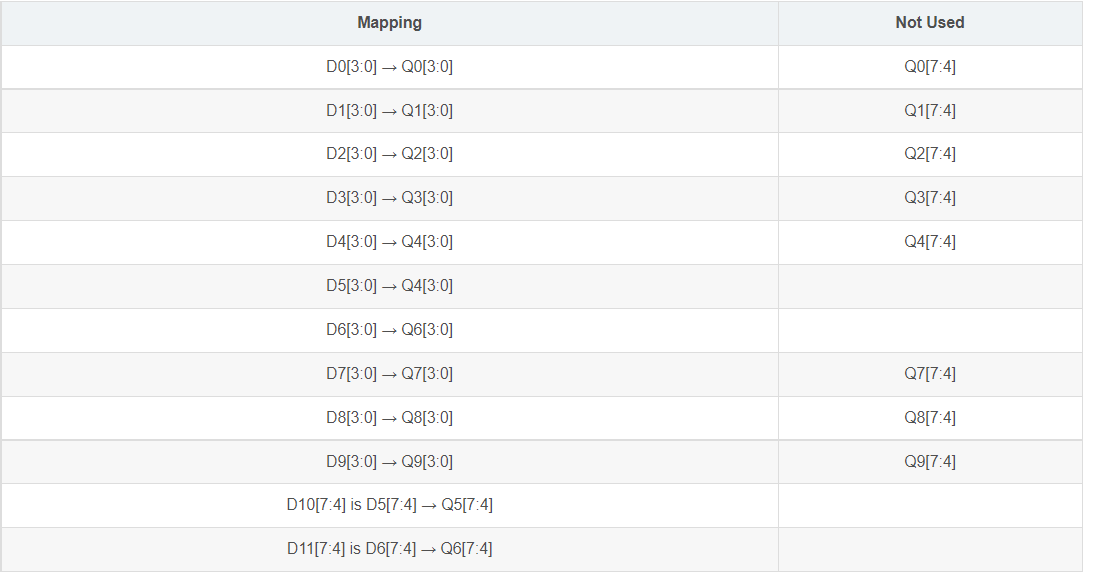

4 x 4 模式——该模式将 FIFO 配置为具有 12 个 4 位宽数据输入 (D) 和 12 个 4 位宽数据输出 (Q)。 D0[3:0] – D9[3:0] 端口映射到 Q0[3:0] – Q9[3:0] 端口。 D5[7:4] 和 D6[7:4] 是两个额外的数据输入端口,用作 D10 和 D11,并映射到 Q5[7:4] 和 Q6[7:4] 输出端口。 其他 D[7:4] 端口未使用。 下表详细显示了 4 x 4 模式映射。

8 x 4 模式——该模式将 FIFO 配置为具有 10 个 8 位宽数据输入 (D) 和 10 个 4 位宽数据输出 (Q)。 在 8 x 4 模式下,输出数据路径中的 2:1 多路复用器将 8 位输入数据串行化为 4 位输出数据宽度。 4 x 8 模式一般是当输出时钟频率是输入时钟频率的两倍,因此输出数据是输入数据宽度的一半时使用。 下表详细显示了 8 x 4 模式映射。

两种模式都支持 FULL、EMPTY、ALMOSTFULL 和 ALMOSTEMPTY 标志。

OUT_FIFO 原语

OUT_FIFO 原语如下图所示。

额外的输入端口 D10 (D5[7:4]) 和 D11 (D6[7:4]) 和输出端口 Q10 (Q5[7:4]) 和 Q11 (Q5[7:4]) 在 4 x 4 模式。

ALMOSTEMPTY、ALMOSTFULL相应的属性可以设置为值 1 或 2。 因此,在标志置位之后发生至少一或两次读取或写入。 由于 FIFO 的异步特性,可能会有一到两次额外的读取或写入,将读取或写入的总数增加到三到四次。

复位 IO_FIFO

一个 IO_FIFO 有一个异步复位,它在内部与读和写时钟域重新同步。 为确保正确复位,在写入 IO_FIFO 之前,必须将 RESET 置为高电平至少四个 RDCLK 或 WRCLK 周期,以较慢者为准。 当 RESET 被断言时,RDEN 和 WREN 必须保持低电平。

IO_FIFO 应保持在复位状态,直到写入和读取时钟都存在且稳定。 类似地,如果在配置之后读取或写入时钟不可用,IO_FIFO 必须如上所述在有效时钟被置位后复位。

EMPTY 和 FULL 标志

FULL 标志置为高电平时,表示 FIFO 内核和输入寄存器都已满。 输出寄存器的状态被忽略。EMPTY 标志指示输出寄存器中数据的状态。 当 EMPTY 标志置为高电平时,输出寄存器中的数据无效。ALMOST EMPTY 和 ALMOST FULL 标志 ALMOSTEMPTY 和 ALMOSTFULL 标志提供了 IO_FIFO 接近其限制的早期指示。 这些标志可以配置为在 IO_FIFO 达到满或空状态之前断言一个或两个周期。 值 1 表示只剩下一个字可以读取或写入。 值 2 表示还有两个字要读取或写入。

由于 IO_FIFO 和内部同步的异步特性,标志可能过于悲观。 在读操作期间,存储的数据可能比 ALMOSTEMPTY 标志输出 1 或 2 指示的多。在写操作期间,可用于写入的空间可能比 ALMOSTFULL 标志输出 1 或 2 指示的多。

ALMOSTEMPTY 和 ALMOSTFULL 标志

不一定与 FULL 和 EMPTY 标志重叠。 可以在 EMPTY 断言之前让 ALMOSTEMPTY 断言和取消断言。 如果 WRCLK 比 RDCLK 快两倍以上,就会发生这种情况。下表总结了所有适用的 IO_FIFO 属性。

reference

- UG471