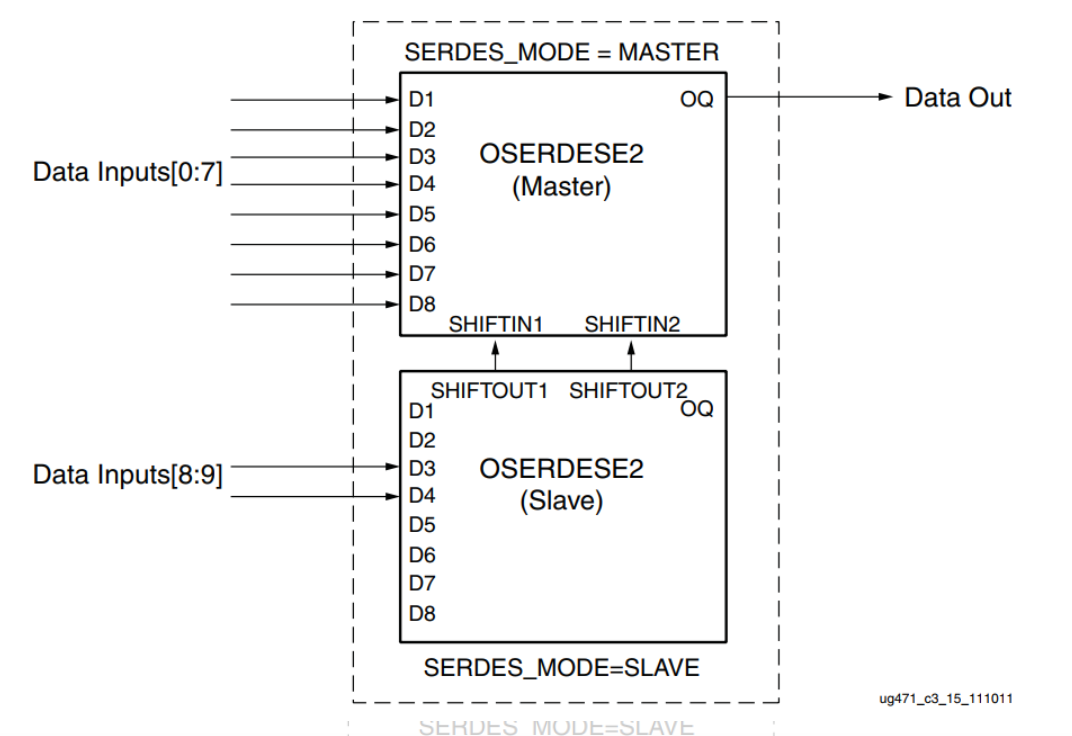

OSERDESE2 宽度扩展

OSERDESE2 模块用于构建大于 8:1 的并串转换器。 在每个 I/O 块中都有两个 OSERDESE2 模块; 一主一从。 通过将主 OSERDESE2 的 SHIFTIN 端口连接到从 OSERDESE2 的 SHIFTOUT 端口,并行到串行转换器可以扩展到高达 10:1 和 14:1(仅限 DDR 模式)。 对于差分输出,主 OSERDESE2 必须位于差分输出对的正极(_P 引脚)侧。 当输出不是差分时,与从机 OSERDESE2 关联的输出缓冲区不可用,也不能使用宽度扩展。

当使用互补的单端标准(例如,DIFF_HSTL 和 DIFF_SSTL)时,可能不使用宽度扩展。 这是因为互补单端标准使用 I/O 块中的两个 OLOGICE2/3 块来传输两个互补信号,没有 OLOGICE2/3 块可用于宽度扩展。

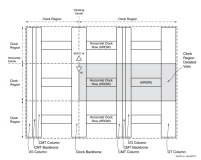

下图显示了使用主从 OSERDESE2 模块的 10:1 DDR 并串转换器的框图。 在这种情况下,端口 D3–D4 用于从属 OSERDESE2 上并行接口的最后两位。

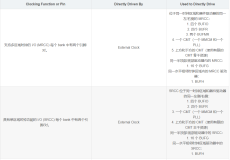

下表列出了 SDR 和 DDR 模式的数据宽度可用性。

| 数据模式 | 可用位宽 |

| SDR Data Widths | 2, 3, 4, 5, 6, 7, 8 |

| DDR Data Widths | 4, 6, 8, 10, 14 |

扩展并串转换器位宽的指南

- OSERDESE2 模块都必须是相邻的主从对。

- 将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,将从 OSERDESE2 设置为 SLAVE。

- 用户必须将 MASTER 的 SHIFTIN 端口连接到 SLAVE 的 SHIFTOUT 端口。

- SLAVE 仅使用端口 D3 到 D8 作为输入。

- Master 和 Slave 的 DATA_WIDTH 相等。

- 属性 INTERFACE_TYPE 设置为 DEFAULT。

用于需要宽度扩展的数据宽度的从输入在表 3-10 中列出。

| Data Width | Slave Inputs Used |

| 10 | D3–D4 |

| 14 | D3–D8 |

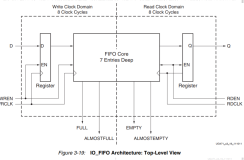

输出反馈 OSERDESE2 引脚 OFB 有两个功能:

- 作为 ISERDESE2 OFB 引脚的反馈路径。

- 作为与ODELAYE2 的连接。 OSERDESE2 的输出可以通过 OFB 引脚路由,然后通过 ODELAYE2 延迟。

OSERDESE2 延迟

默认接口类型延迟

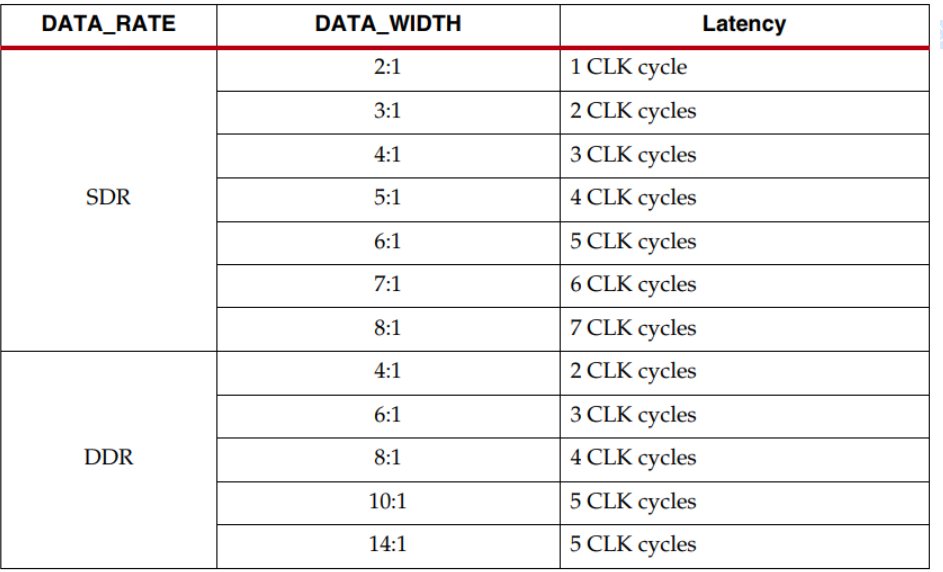

OSERDESE2 块的输入到输出延迟取决于 DATA_RATE 和 DATA_WIDTH 属性。 延迟定义为以下两个事件之间的时间段:

- 当 CLKDIV 的上升沿将输入 D1-D8 处的数据输入 OSERDESE2 时;

- 当串行流的第一位出现在 OQ 时。

下表总结了各种 OSERDESE2 延迟值。CLK 和 CLKDIV 时钟边沿通常不是相位对齐的。 当两个时钟的边沿相位对齐时,延迟可以变化一个周期。

OSERDESE2 时序模型和参数

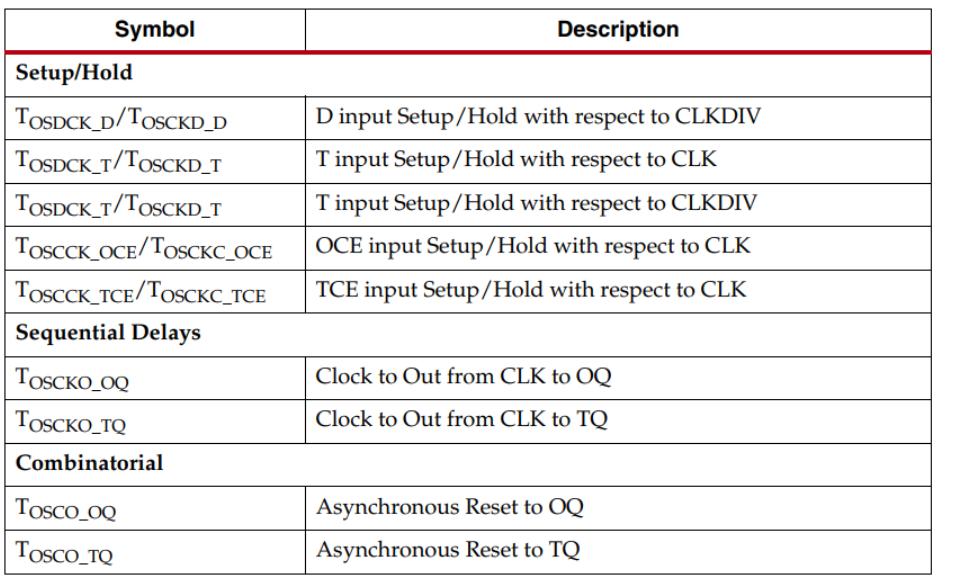

下面讨论与 OSERDESE2 原语相关的所有时序模型。

下表描述了 7 系列 FPGA 数据手册中 OSERDESE2 开关特性的功能和控制信号。

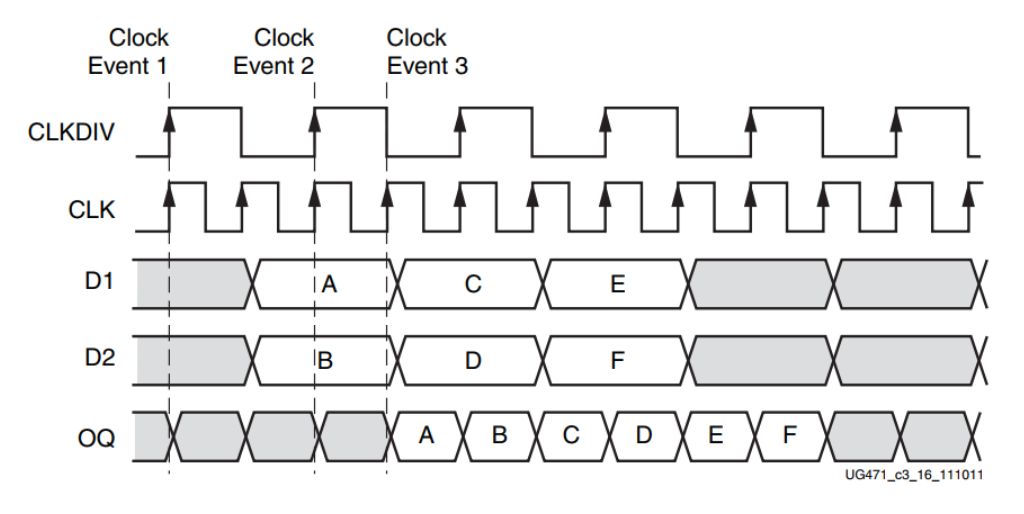

2:1 SDR 串行化的时序特性

下图显示了 2:1 SDR 数据串行化的时序。

时钟事件 1

在 CLKDIV 的上升沿,字 AB 被从 FPGA 逻辑驱动到 OSERDESE2 的 D1 和 D2 输入(经过一些传播延迟)。

时钟事件 2

在 CLKDIV 的上升沿,字 AB 从 D1 和 D2 输入采样到 OSERDESE2。

时钟事件 3

在 AB 被采样到 OSERDESE2 之后的一个 CLK 周期后,数据位 A 出现在 OQ。 该延迟与表中列出的 2:1 SDR 模式 OSERDESE2 一个 CLK 周期的延迟一致。

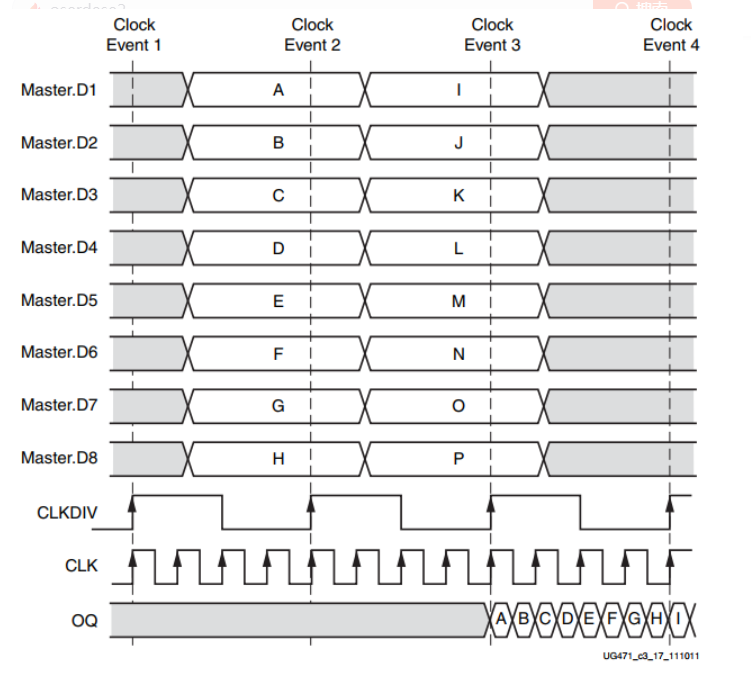

8:1 DDR 串行化的时序特性

下图说明了 8:1 DDR 数据串行化的时序。 与需要级联的前几代相比,所有八个位都连接到主 OSERDESE2 的 D1-D8。

时钟事件 1

在 CLKDIV 的上升沿,字 ABCDEFGH 从 FPGA 逻辑驱动到 OSERDESE2 的 D1-D8 输入。

时钟事件 2

在 CLKDIV 的上升沿,字 ABCDEFGH 从 D1–D8 被采样到 OSERDESE2。

时钟事件 3

在将 ABCDEFGH 采样到 OSERDESE2 之后,数据位 A 出现在 OQ 四个 CLK 周期。 此延迟与表中列出的 8:1 DDR 模式 OSERDESE2 延迟的四个 CLK 周期一致。

第二个word IJKLMNOP 从 D1-D8 采样到 OSERDESE2。

时钟事件 4

在时钟事件 3 和 4 之间,整个字 ABCDEFGH 在 OQ 上串行传输,在一个 CLKDIV 周期内传输总共 8 位。

在 IJKLMNOP 被采样到 OSERDESE2 之后,数据位 I 出现在 OQ 四个 CLK 周期。 此延迟与表中列出的 8:1 DDR 模式 OSERDESE2 延迟的四个 CLK 周期一致。

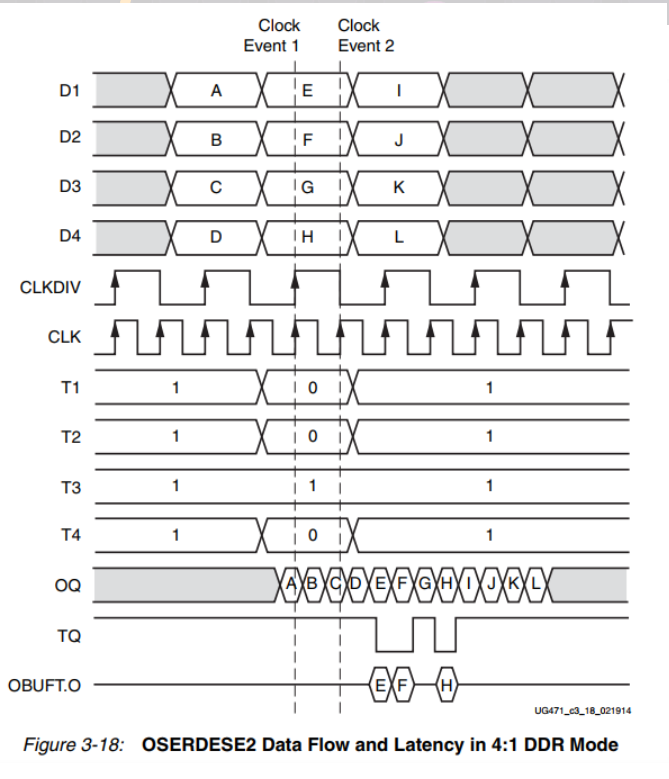

4:1 DDR 三态控制器串行化的时序特性

三态控制器的操作如下图所示。 该示例是双向系统中显示的 4:1 DDR 情况,其中 IOB 必须经常为 3 态。

时钟事件 1

T1、T2 和 T4 被驱动为低电平以释放三态条件。 OSERDESE2 中的 T1–T4 和 D1–D4 的串行化路径是相同的(包括延迟),因此 EFGH 位始终与时钟事件 1 期间出现在 T1–T4 引脚的 0010 对齐。

时钟事件 2

在 EFGH 被采样到 OSERDESE2 之后,数据位 E 出现在 OQ 一个 CLK 周期。

此延迟与表中列出的 4:1 DDR 模式 OSERDESE2 延迟一个 CLK 周期一致。

时钟事件 1 期间 T1 的三态位 0 出现在 TQ 一个 CLK 周期后,0010 被采样到 OSERDESE2 三态模块。 此延迟与表中列出的 4:1 DDR 模式 OSERDESE2 延迟一个 CLK 周期一致。

reference

- UG471