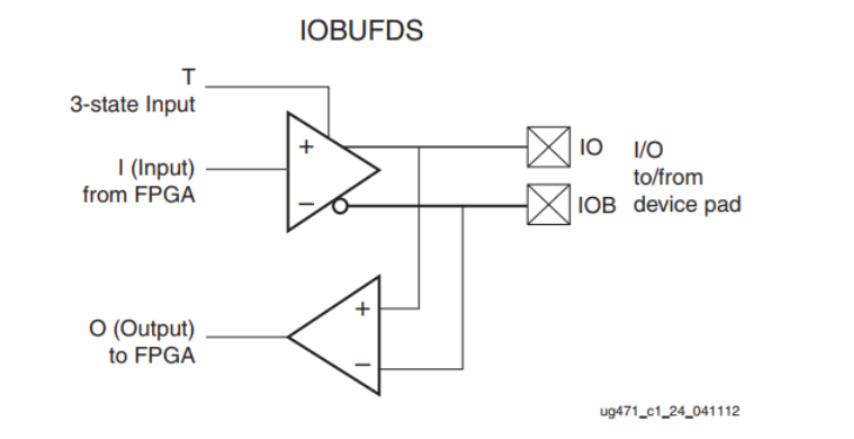

IOBUFDS

下图显示了差分输入/输出缓冲器原语。 T引脚上的逻辑高电平禁用输出缓冲器。

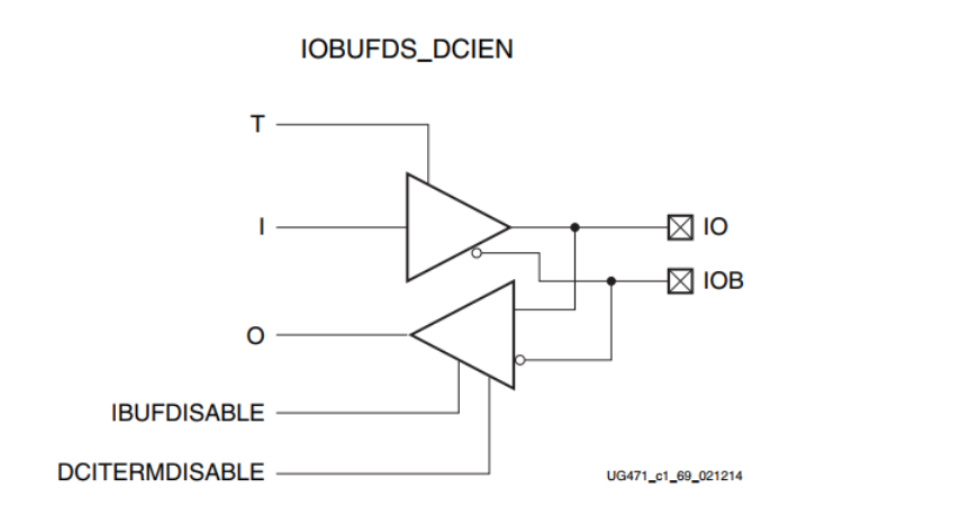

IOBUFDS_DCIEN

下图所示的 IOBUFDS_DCIEN 原语在 HP I/O bank 中可用。 它有一个 IBUFDISABLE 端口,可用于在不使用缓冲区期间禁用输入缓冲区。 IOBUFDS_DCIEN 原语还有一个 DCITERMDISABLE 端口,可用于手动禁用可选的 DCI 拆分终止功能。 有关详细信息,请参阅拆分终端 DCI(戴维宁等效终端到 VCCO/2)和 DCI 和三态 DCI (T_DCI)。

当 USE_IBUFDISABLE 属性设置为 TRUE 并且 IBUFDISABLE 信号置为高电平时,IOBUFDS_DCIEN 原语可以禁用输入缓冲器并强制到架构的 O 输出为逻辑高电平。 如果 USE_IBUFDISABLE 设置为 FALSE,此输入将被忽略并应接地。 如果 I/O 使用分离端接 DCI 功能,则只要 DCITERMDISABLE 信号被置为高电平,该原语就会禁用端接支路。 只有三态 DCI I/O 标准可用于双向信号。

使用三态 DCI I/O 标准,只要驱动器处于活动状态,DCI 终端支路就会关闭。 IOBUFDS_DCIEN 原语还允许在 DCITERMDISABLE 信号被置为高电平时禁用终端支路。 只要输入空闲一段时间,这些功能就可以结合起来降低功耗。

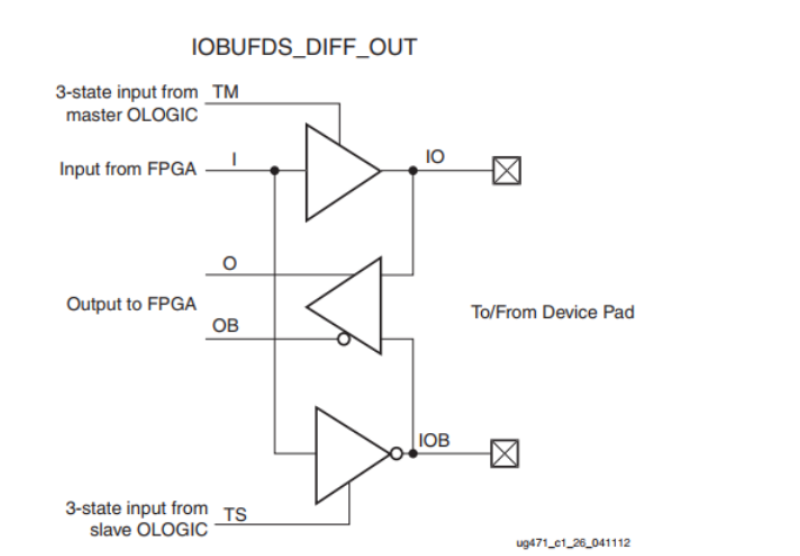

IOBUFDS_DIFF_OUT

下图显示了具有互补输出(O 和 OB)的差分输入/输出缓冲器原语。 此原语仅推荐给经验丰富的 Xilinx 设计人员使用存储器接口应用。 T 引脚上的逻辑高电平禁用输出缓冲器。

IOBUFDS_DIFF_OUT_DCIEN

下图所示的 IOBUFDS_DIFF_OUT_DCIEN 原语在 HP I/O bank 中可用。 它具有互补差分输出、一个 IBUFDISABLE 端口,可用于在不使用缓冲区期间禁用输入缓冲区,以及一个 DCITERMDISABLE 端口,可用于手动禁用可选的 DCI 分离终端功能。

当 USE_IBUFDISABLE 属性设置为 TRUE 且 IBUFDISABLE 信号置为高电平时,IOBUFDS_DIFF_OUT_DCIEN 原语可以禁用输入缓冲器并强制 O 和 OB 输出到结构高电平。 如果 USE_IBUFDISABLE 设置为 FALSE,此输入将被忽略并应接地。 如果 I/O 正在使用分离端接 DCI 功能,只要 DCITERMDISABLE 信号被置为高电平,该原语就会禁用端接支路。 只有三态 DCI I/O 标准可用于双向信号。 对于三态 DCI I/O 标准,只要驱动器处于活动状态,DCI 终端支路就会关闭(对于 IO 输出,TS 为低电平,对于 IOB 输出,TM 为低电平)。 IOBUFDS_DIFF_OUT_DCIEN 原语还允许在 DCITERMDISABLE 信号被置为高电平时禁用终端支路。 只要输入空闲一段时间,这些功能可以结合起来降低功耗。

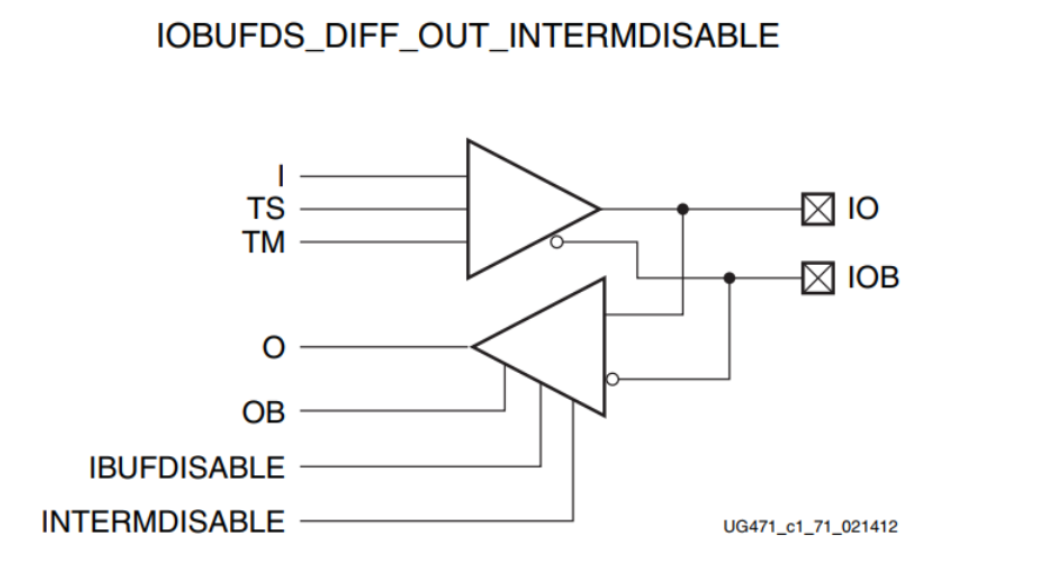

IOBUFDS_DIFF_OUT_INTERMDISABLE

下图所示的 IOBUFDS_DIFF_OUT_INTERMDISABLE 原语在 HR I/O bank 中可用。 它有一个 IBUFDISABLE 端口,可用于在不使用缓冲区期间禁用输入缓冲区。IOBUFDS_DIFF_OUT_INTERMDISABLE 原语还有一个 INTERMDISABLE 端口,可用于禁用可选的未校准拆分终止功能。

当 USE_IBUFDISABLE 属性设置为 TRUE 且 IBUFDISABLE 信号置为高电平时,IOBUFDS_DIFF_OUT_INTERMDISABLE 原语可以禁用输入缓冲区并强制 O 和 OB 输出到结构高电平。 如果 USE_IBUFDISABLE 设置为 FALSE,此输入将被忽略并应接地。 如果 I/O 使用可选的未校准分离端接功能 (IN_TERM),则只要驱动器处于活动状态,这些端接脚也会被禁用(IO 输出的 TS 为低电平,IOB 输出的 TM 为低电平)。 IOBUFDS_DIFF_OUT_INTERMDISABLE 原语还允许在 INTERMDISABLE 信号被置为高电平时禁用终端支路。只要输入空闲一段时间,这些功能就可以结合起来降低功耗。

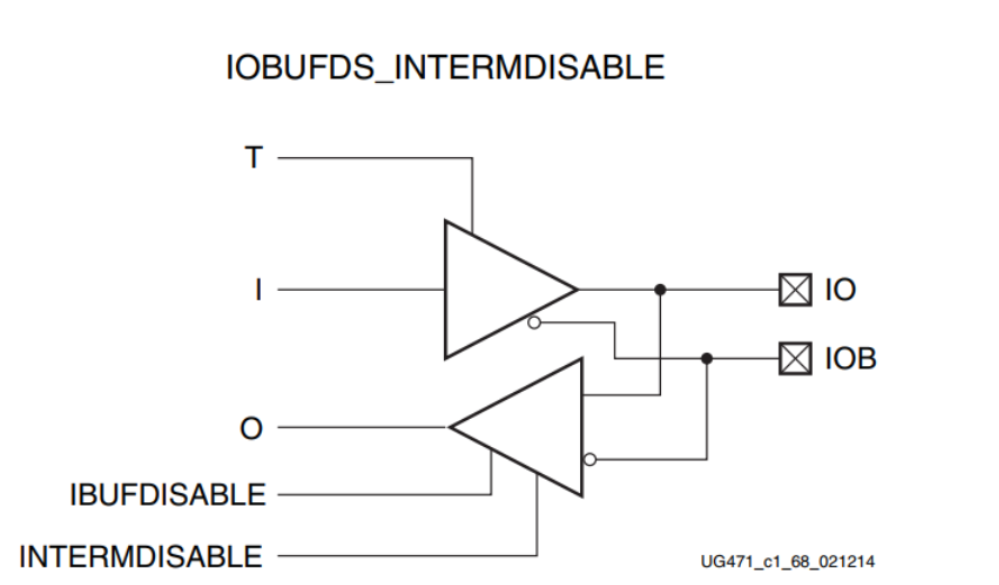

IOBUFDS_INTERMDISABLE

下图所示的 IOBUFDS_INTERMDISABLE 原语在 HR I/O bank 中可用。 它有一个 IBUFDISABLE 端口,可用于在不使用缓冲区期间禁用输入缓冲区。 IOBUFDS_INTERMDISABLE 原语还有一个 INTERMDISABLE 端口,可用于禁用可选的未校准拆分终端功能。

当 USE_IBUFDISABLE 属性设置为 TRUE 且 IBUFDISABLE 信号置为高电平时,IOBUFDS_INTERMDISABLE 原语可以禁用输入缓冲器并强制到架构的 O 输出为逻辑高电平。 如果 USE_IBUFDISABLE 设置为 FALSE,此输入将被忽略并应接地。 如果 I/O 使用可选的未校准拆分终端功能 (IN_TERM),则只要驱动器处于活动状态(T 为低电平),这些终端脚就会被禁用。 该原语还允许在 INTERMDISABLE 信号被置为高电平时禁用终端支路。 只要输入空闲一段时间,这些功能就可以结合起来降低功耗。

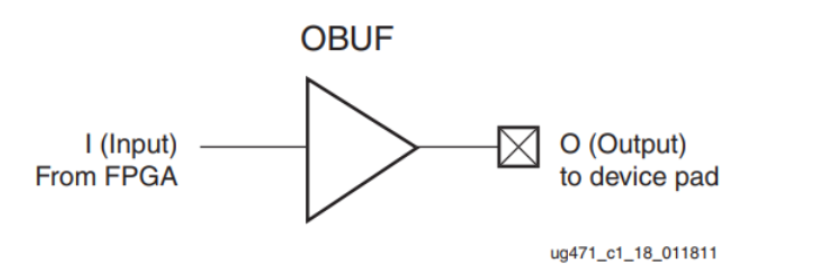

OBUF

必须使用输出缓冲器 (OBUF) 将信号从 7 系列器件驱动到外部输出焊盘。 通用 7 系列 FPGA OBUF 原语如下图所示。

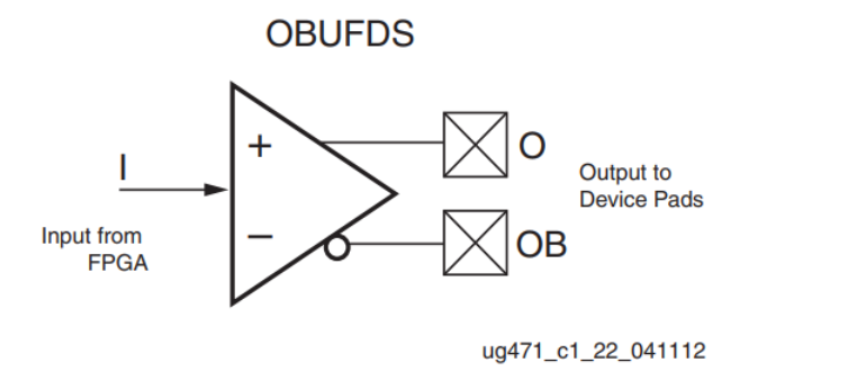

OBUFDS

下图显示了差分输出缓冲器原语。

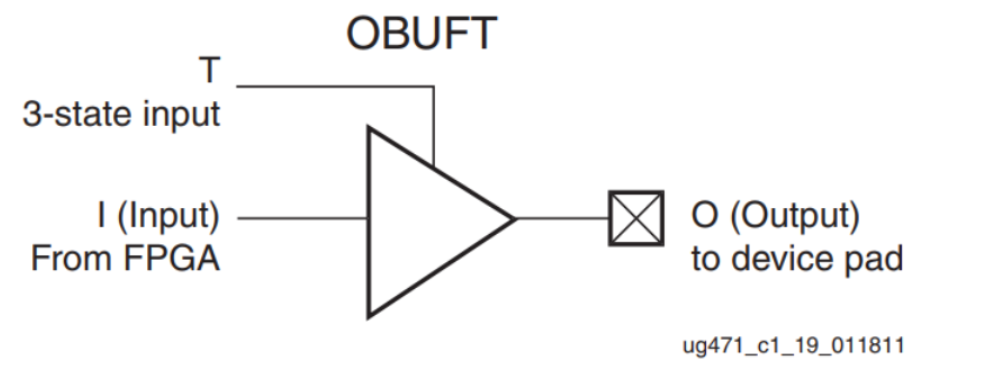

OBUFT

下图所示的通用三态输出缓冲器 OBUFT 通常实现三态输出或双向 I/O。

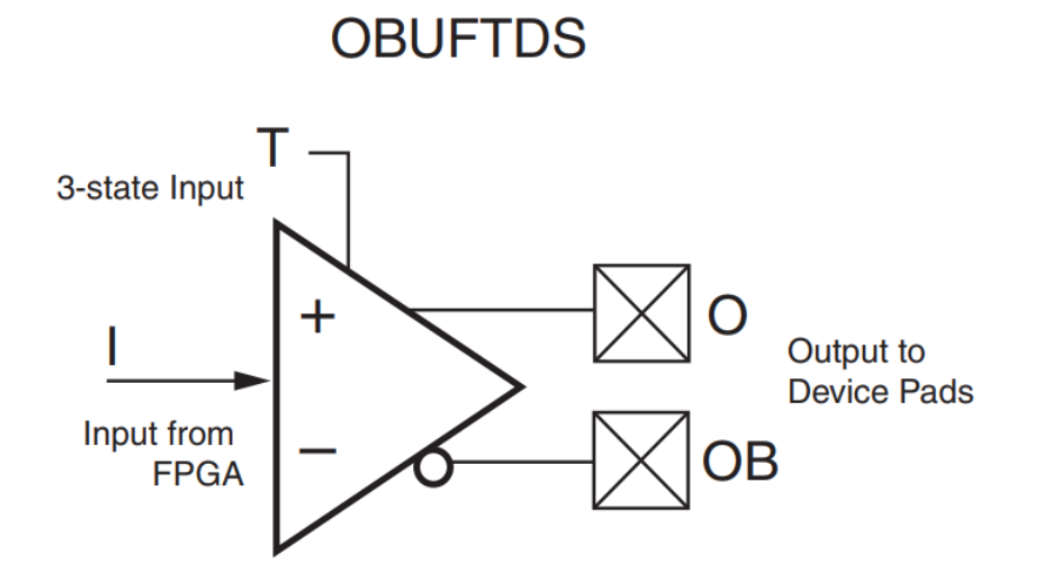

OBUFTDS

下图显示了差分三态输出缓冲器原语。

reference

- UG471